#### The Real-Time Producer/Consumer Paradigm: Towards Verifiable Real-Time Computations

#### Kevin Jeffay

Technical Report # 89-09-15

Department of Computer Science and Engineering, FR-35 University of Washington, Seattle, WA 98195 USA September, 1989

A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy University of Washington 1989

#### The Real-Time Producer/Consumer Paradigm: Towards Verifiable Real-Time Computations

#### Kevin Jeffay

Technical Report # 89-09-15

Department of Computer Science and Engineering, FR-35 University of Washington, Seattle, WA 98195 USA September, 1989

> A dissertation submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy University of Washington 1989

#### University of Washington

#### Abstract

# The Real-Time Producer/Consumer Paradigm: Towards Verifiable Real-Time Computations

by Kevin Jeffay

Chairperson of the Supervisory Committee: Professor Alan C. Shaw

Department of Computer Science and

Engineering

Real-time computer systems are loosely defined as the class of computer systems that perform computations and I/O operations in a time frame defined by processes in the external environment. Within this class of systems are hard-real-time systems. Hard-real-time systems are characterized by the existence of timing constraints that must be strictly adhered to for the system to function correctly. In this dissertation we study the problem of designing and analyzing hard-real-time systems. A message passing discipline for designing hard-real-time systems is developed. The discipline consists of (1) a graphical notation for specifying the logical structure of systems, (2) an operational semantics for reasoning about the real-time behavior of the system, and (3) a formal implementation model.

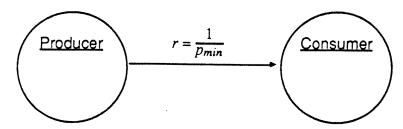

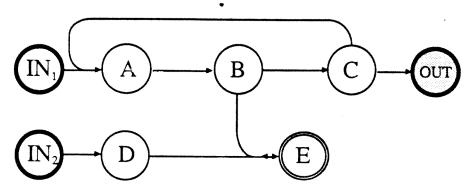

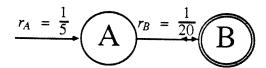

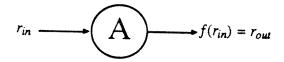

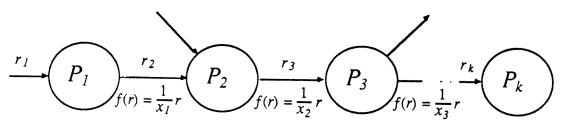

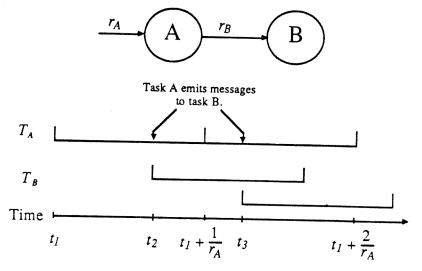

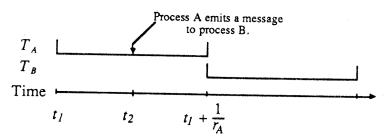

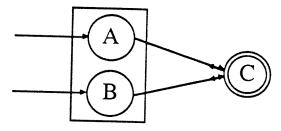

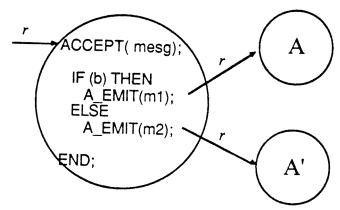

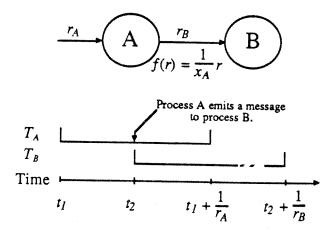

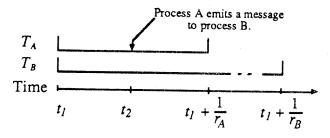

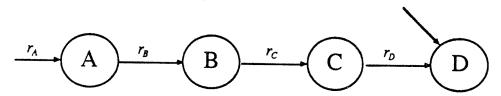

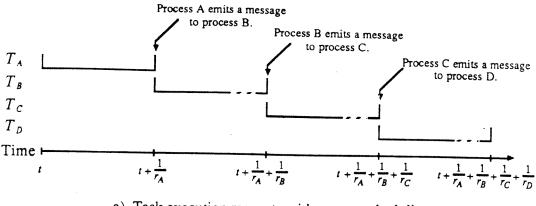

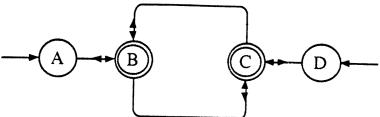

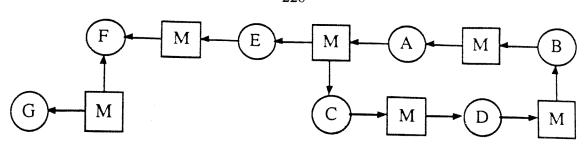

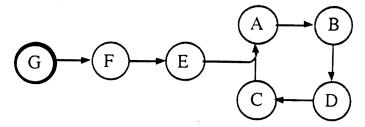

A design is a directed graph in which vertices are program components and edges are communication channels. Program components communicate by sending messages on unidirectional channels. We develop a novel semantics of communication based on a paradigm of process interaction called the *real-time producer/consumer paradigm*. For each message sender, these semantics specify the rate at which messages are consumed. With these semantics the real-time behavior of the designed system is completely understood in terms of the rates at which messages are sent.

We present a formal implementation model for our discipline based on periodic and sporadic tasks. The model is developed to study complexity and optimality issues concerning the implementation of designs constructed using our discipline. For this model

we investigate several uniprocessor scheduling and synchronization problems. New results on the optimal, non-preemptive, scheduling of periodic and sporadic tasks are developed. We introduce the concept of an *implementation strategy* to deal with tasks that share resources. An implementation strategy consists of the integration of a scheduling and synchronization policy. For our formal model we demonstrate that optimal implementation strategies based on *earliest deadline first* scheduling and WAIT and BROADCAST synchronization exist. The analysis of these scheduling and synchronization problems yield a decision procedure that can efficiently determine if an arbitrary acyclic, and some cyclic, design graphs can be guaranteed to adhere to the specifications derived from the real-time producer/consumer paradigm.

Some paper designs of actual systems, and a prototype programming system based on our discipline, demonstrate the viability of our research. They show that our design discipline is expressive enough to describe the real-time behavior of actual systems and yet is simple enough to allow rigorous analysis of the real-time behavior of systems so designed.

## Table of Contents

| Lis<br>Lis | t of Figures Page t of Tables X                                                                                                                                         | _      |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------|

| Ch         | apter 1: Introduction                                                                                                                                                   |        |

| 1.1        | 1.1.1 Real-Time Systems and a Spectrum of Peal Time Community                                                                                                           |        |

| 1.2<br>1.3 | Research Approach and Contributions                                                                                                                                     |        |

|            | 1.3.2 Design Methodologies                                                                                                                                              |        |

| 1.4        | 1.3.5 Summary                                                                                                                                                           | 1      |

| •••        | Thesis Overview                                                                                                                                                         | 3      |

| Ch:<br>Tin | apter 2: A Message Passing Design Discipline For Hard-Rea<br>ne Systems                                                                                                 | 1-     |

| 2.1<br>2.2 | Introduction                                                                                                                                                            | 5      |

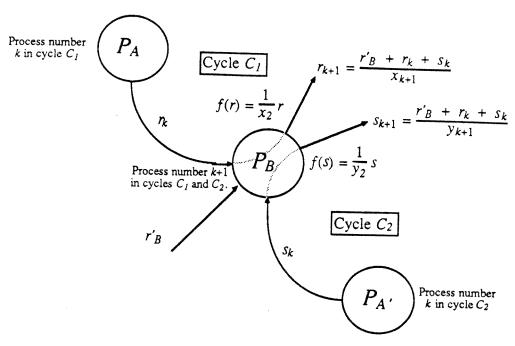

|            | An Origin of Timing Constraints 17  2.2.1 Producer/Consumer Systems 17  2.2.2 Real-Time Producer/Consumer Systems 19  2.2.3 The Real-Time Producer/Consumer Paradiam 19 | 7<br>3 |

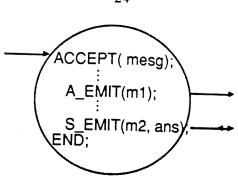

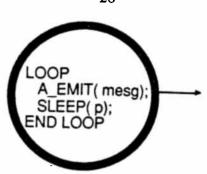

| 2.3        | System Components and Graphical Notation                                                                                                                                |        |

|            | 2.3.3 Input Devices                                                                                                                                                     |        |

| 2.4        | 2.3.5 Channels                                                                                                                                                          |        |

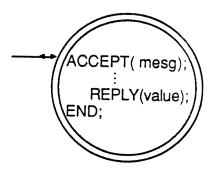

| 2.5        | Message Passing Semantics                                                                                                                                               |        |

|            | 2.5.3 Synchronous Channel Semantics 32                                                                                                                                  |        |

|            | 2.5.4 Mutual Exclusion                                                                                                                                                  |        |

| 2.6        | Computing Message Transmission Rates                                                    |

|------------|-----------------------------------------------------------------------------------------|

|            | 2.6.2 Determining Message Input Rates                                                   |

|            | 2.6.3 Computing Channel Transmission Rates                                              |

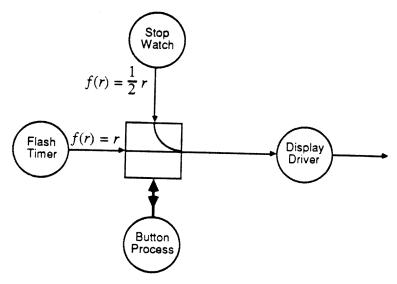

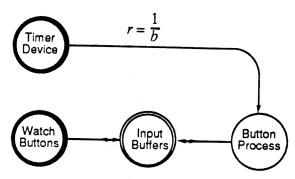

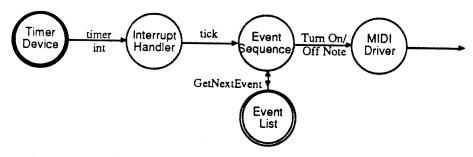

| 2.7        | An Example: A Digital Stopwatch 39                                                      |

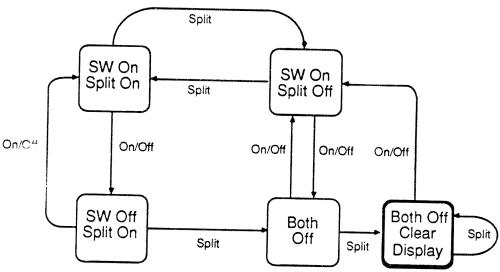

| ,          | 2.7.1 Functional Description                                                            |

|            | 2.7.1 Functional Description 40                                                         |

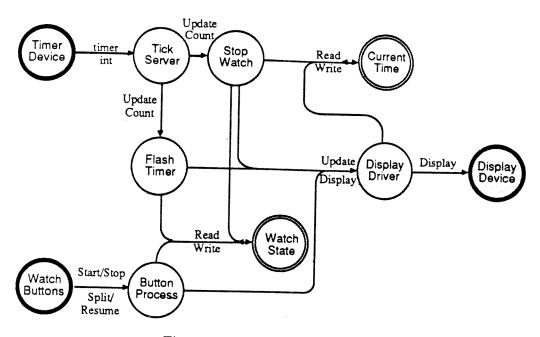

|            | 2.7.2 Proposed Design 41                                                                |

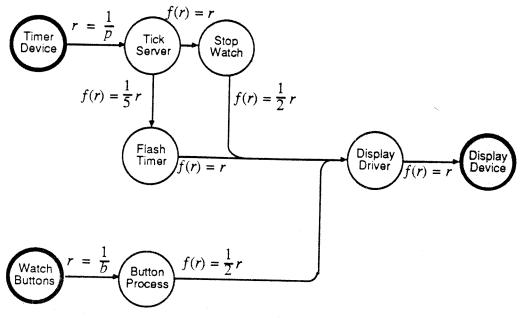

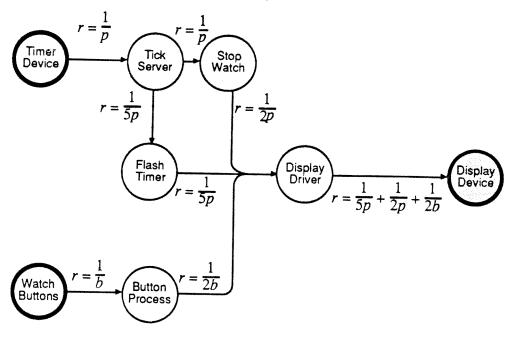

| 2 8        | 2.7.3 Delivation of Message Hamming Raise                                               |

| 2.0        | Reasoning About Time                                                                    |

|            | 2.8.1 Message Propagation Times Through Processes                                       |

|            | 2.8.2 Message Propagation for Output Devices                                            |

| 2.9        | 2.8.3 An Example: Reasoning about the Stopwatch                                         |

| 4.9        | Discussion and Summary                                                                  |

|            |                                                                                         |

|            |                                                                                         |

| Ch         | onton 2. Fundamental Calcil II. D. J. W. G. J.                                          |

| CII        | apter 3: Fundamental Scheduling Results For Cyclic Tasks                                |

| 3.1        | Introduction                                                                            |

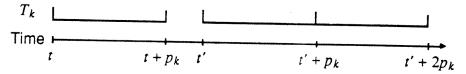

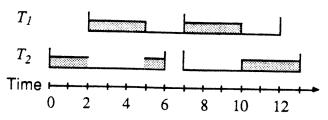

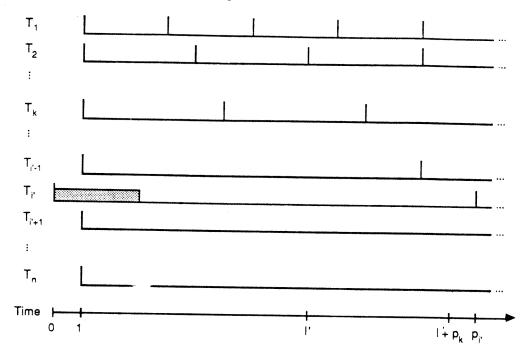

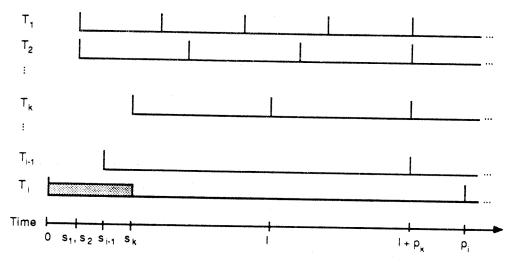

| 3.2        | Basic Task Model, Notation, and Approach                                                |

|            | 3.2.1 Cyclic Tasking Model                                                              |

|            | 3.2.2 On-line Versus Off-line Scheduling 58                                             |

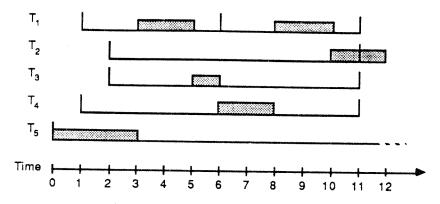

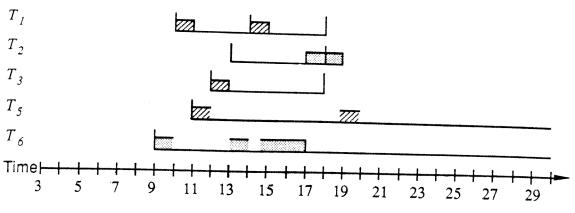

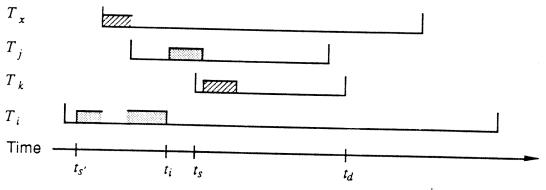

|            | 3 2 3 Scheduling Diagrams                                                               |

|            | 3.2.3 Scheduling Diagrams                                                               |

| 3.3        | 3.2.4 Approach 60 The Farliest Deadling First Schoduling Policy                         |

| 3.4        | The Earliest Deadline First Scheduling Policy                                           |

| 3.5        | Bounding Processor Demand 61                                                            |

| 3.6        | Preemptive Scheduling of Periodic and Sporadic Tasks                                    |

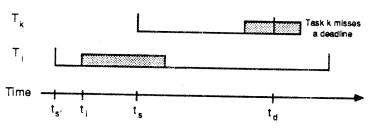

| 5.0        | Non-Preemptive Scheduling of Sporadic Tasks                                             |

|            | J.U. I INCCESSARY CONDITIONS for Beasthility (CO.)                                      |

|            | 3.0.2 The Optimality of the EDF Discipline For All Possible Release                     |

|            | 1 III. 274                                                                              |

| 2 77       | 3.6.3 The Optimality of the EDF Discipline For Arbitrary Release Times 80               |

| 3.7        | Complexity of Deciding Feasibility For Sporadic Tasks on                                |

| 3.8        | Suiculling with inserior interrime                                                      |

| 3.9        | INUIT-FICE INDIES OF SCHEDILING OF PERIODIC Tasks                                       |

| 3.10       | Discussion and Summary91                                                                |

|            |                                                                                         |

|            |                                                                                         |

| ~          |                                                                                         |

| Cha        | pter 4: An Implementation Strategy For Sporadic Tasks With                              |

| Sha        | red Resources                                                                           |

|            |                                                                                         |

| 4.1        | Introduction                                                                            |

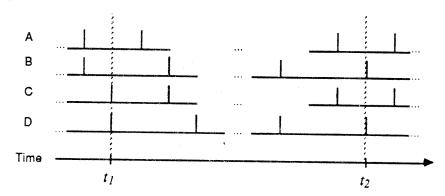

| 4.2        | A Tasking Model With Shared Resources                                                   |

|            | 4.2.1 Senally Kellsable resources                                                       |

|            | 4.2.2 Absolute and Relative Feasibility                                                 |

| 4.3        | Implementation Strategy Definition                                                      |

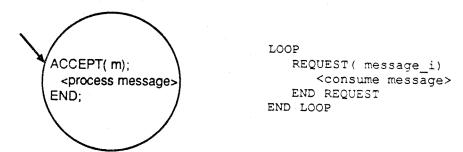

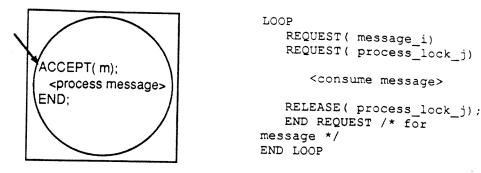

| -          | 4.3.1 Programming Model and Synchronization Discipline                                  |

|            | 4.3.2 Processor Scheduling Discipline                                                   |

| 4.4        | Single Resource Single Phase Systems                                                    |

| 4.5        | Single Resource, Single Phase Systems. 101  Multiple Resource Single Phase Systems. 101 |

| 4.5<br>4.6 | Multiple Resource, Single Phase Systems 175                                             |

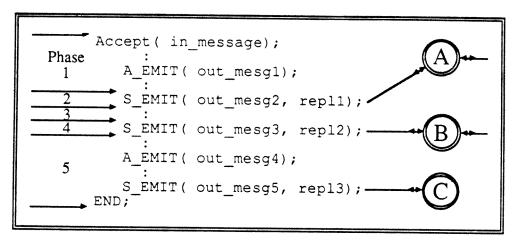

| ₹.0        | Multiple Phase Systems                                                                  |

|            | 4.0.1 From Multiple Phase Tasks to Single Phase Tasks                                   |

|             | 4.6.2 Single Resource, Multiple Phase Tasks 4.6.3 Multiple Resource, Multiple Phase Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|-------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4.7         | 4.6.3 Multiple Resource, Multiple Phase Tasks                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|             | 4.7.1 Desirable Interactions Between Scheduling and Synchronization                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             | 4.7.2 Bounding the Programming D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | 4.7.3 Feasibility Versus Processor Utilization: Comparison with 116                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 4.8         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 119                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| Ch          | apter 5: Realizing the Real-Time Producer/Consumer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|             | radigm                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| * 4         | i duigni                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 5.1         | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 5.2         | 101                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

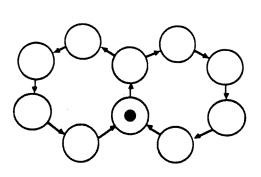

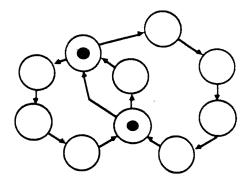

|             | 5.2.1 Disjoint Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| •           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|             | 137                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| J. <b>4</b> | Reasoning About Time Revisited. 140 5.4.1 Single Processor Implementations 142                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|             | The street of th |

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5         | Model Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|             | Model Extensions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| = (         | The state of the s |

| 5.6         | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

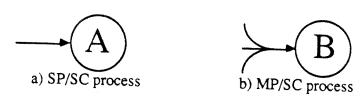

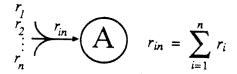

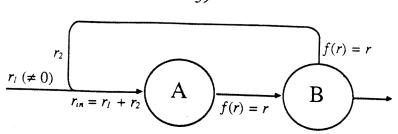

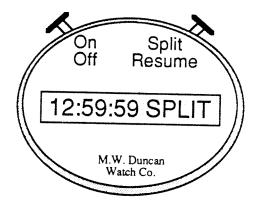

|             |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |