# Pin Assignment for Multi-FPGA Systems

Scott Hauck, Gaetano Borriello Department of Computer Science and Engineering University of Washington Seattle, WA 98195

# Abstract

There is currently great interest in using systems of FPGAs for logic emulators, custom computing devices, and software accelerators. An important step in making these technologies more generally useful is to develop completely automatic mapping tools from high-level specification to FPGA programming files. In this paper we examine one step in this automatic mapping process, the selection of physical FPGA pins to use for routing inter-FPGA signals. We present an algorithm that greatly increases mapping speed while also improving mapping quality.

## Introduction

In the time since they were introduced, FPGAs have moved from being viewed simply as a method of implementing random logic in circuit boards to being a flexible implementation medium for many types of systems. Logic emulation tasks, where ASIC designs are simulated on large FPGA-based structures [Varghese93], have greatly increased simulation speeds. Software subroutines have been hand-optimized to FPGAs to speed up inner loops of programs [Bertin93], and work has been done to automate this process [Wazlowski93]. FPGA-based circuit implementation boards have been developed for easier project construction in electronics education [Chan92, Chan93]. Custom-computing devices built from FPGAs have demonstrated significant performance improvements over standard general-purpose processors [Lopresti91, Arnold93]. An important aspect shared by all of these systems is that they harness multiple FPGAs, connected in a fixed routing structure, to perform their tasks. While the FPGAs themselves can be routed and rerouted, the wires moving signals between FPGA pins are fixed by the routing structure on the implementation board.

While some very impressive results have been achieved by hand-mapping of algorithms and circuits to FPGA systems, developing a completely automatic system for mapping to these structures is important to achieving more widespread utility. A good example of this are the Quickturn systems [Varghese93], which offer an integrated approach for mapping ASIC circuits. In general, an automatic mapping approach will go through five phases, in the following order: Synthesis, Partitioning/Global Placement, Global Routing, FPGA Place, FPGA Route. During the Synthesis step, the circuit to be implemented is converted from its source format into a netlist appropriate for implementation in FPGAs, possibly after several optimization steps. Partitioning and Global Placement breaks this mapping into subcircuits that will fit into the individual FPGAs, and determines which FPGAs a given subcircuit will occupy. Signals that connect logic in different FPGAs are then routed during Global Routing, which determines both which intermediate FPGAs a signal will move through (if any), as well as what FPGA I/O pins it

will use. With the logic assigned and the inter-FPGA signals routed, standard FPGA Place and Route software can then produce programming files for the individual FPGAs.

For the rest of this paper, we will examine the Global Routing stage of the automatic mapping process. It is important to remember during the following sections the context we are working in: we are mapping to a fixed structure of FPGAs, where wiring between the pins of the FPGAs are prewired, and while the logic has been partitioned to the individual FPGAs, these individual FPGA mappings have not yet been placed nor routed.

# **Global Routing For Multi-FPGA Systems**

The Global Routing phase of mapping to multi-FPGA systems bears a lot of similarity to routing for individual FPGAs, and hopefully similar algorithms can be applied to both problems. Just as in single FPGAs, Global Routing needs to route signals on a fixed topology, with strictly limited resources, while trying both to accommodate high-density mappings and minimize clock periods.

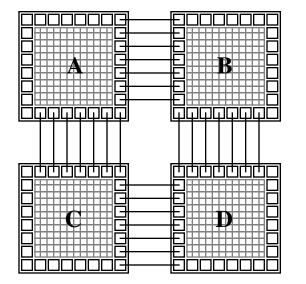

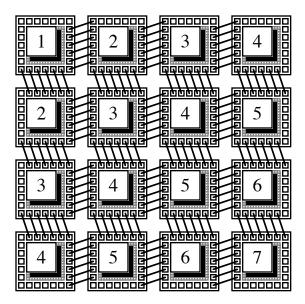

The obvious method for applying single-FPGA routing algorithms to multi-FPGA systems is to view the FPGAs as complex entities, explicitly modelling both internal routing resources and pins connected by individual external wires (figure 1 left). A standard routing algorithm would then be used to determine both which intermediate FPGA to use for long distance routing (i.e., a signal from FPGA A to D would be assigned to use either FPGA B or C), as well as which individual FPGA pins to route through. Unfortunately, this approach will not work. The problem is that although the logic has been already assigned to FPGAs during partitioning, the placement of logic into individual logic blocks will not be done until the next step, FPGA placement. Thus, since there is no specific source or sink for the individual routes, standard routing algorithms cannot be applied.

**Figure 1.** Two views of the inter-FPGA routing problem: As a complex graph including internal resources (left), and a more abstract graph with FPGAs as nodes (right).

The approach we will take here is to abstract entire FPGAs into single nodes in the routing graph, with the arcs between the nodes representing bundles of wires. This solves the unassigned source and sink problem mentioned above, since while the logic hasn't been placed into individual logic blocks, partitioning has assigned the logic to the FPGAs. It also simplifies the routing problem, since the graph is much simpler, and similar resources are grouped together (i.e. all wires connecting the same FPGAs are grouped together into a single edge in the graph). Unfortunately, the routing algorithm can no longer determine the individual FPGA pins a signal should use, since those details have been abstracted away. It is this problem, the assignment of interchip routing signals to FPGA I/O pins, that the rest of this paper addresses.

## Pin Assignment For Multi-FPGA Systems

One solution to the pin assignment problem is quite simple: ignore it. After Global Routing has routed signals through intermediate FPGAs, those signals are then randomly assigned to individual pins. While this simple approach can quickly generate an assignment, it gives up some optimization opportunities. A poor pin assignment can not only result in greater delay and lower logic density, but can also slow down the placement and routing software, which must deal with a more complex mapping problem.

A second solution is to use a topology that simplifies the problem. Specifically, topologies such as bipartite graphs only connect logic carrying FPGAs with routing-only FPGAs. In this way, the logic-bearing FPGAs can be placed initially, and it is assumed that the routing-only FPGAs can handle any possible pin assignment. More details on such an approach can be found in [Chan93]. However, it is important to note that these approaches only apply to topologies such as bipartite graphs and partial crossbars, topologies where logic-bearing FPGAs are not directly connected.

A third approach is to allow the FPGA placement tool to determine its own assignment. This requires that the placement tool allow the user to restrict the locations where an I/O pin can be assigned (e.g., the Xilinx APR and PPR placement and routing tools [Xilinx93]). With such a system, I/O signals are restricted to only those pin locations that are wired to the proper destinations. Once the placement tool determines the pin assignment for one FPGA, this assignment is propagated to the attached FPGAs. It is important to note that this does limit the number of placement runs that can be performed in parallel. Specifically, since the assignment from one FPGA is propagated to adjacent FPGAs only after that entire FPGA has been placed, no two adjacent FPGAs can be placed simultaneously. Since the placement and routing steps can be the most time-consuming steps in the mapping process, achieving the greatest parallelism in this task can be critical. An algorithm for achieving the highest parallelism during placement, while allowing the placement tool to determine the pin assignment, is to find a minimum graph coloring of the FPGAs in the routing graph (since the structure of a multi-FPGA system is usually predefined, the coloring can be precomputed, and thus the inefficiency of finding a graph coloring is not important). Then, all the FPGAs assigned the same color can be placed at the same time, since any FPGAs that are adjacent cannot be assigned the same color. For example, in a four-way mesh (every FPGA is connected to the FPGA

directly adjacent horizontally and vertically), the FPGAs could be placed in a checkerboard pattern, with half handled in the first iteration, and half in the second. Note that since the pin assignment will be determined during placement, the FPGA routing can be run in parallel with other placement or routing. To make sure this is done the most efficiently, FPGAs should be placed in order of the number of FPGAs assigned a given color, from greatest to least. In this way, FPGA routing tasks can be started as soon as possible.

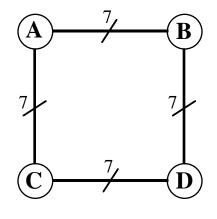

Figure 2. Example problem with the Checkerboard algorithm

One problem with the maximum parallelism (or "checkerboard") method just described is that while the pin assignment for the FPGAs placed first will be very good, since the placer is mostly free in its placement choices, other FPGAs may be placed fairly poorly. For example, consider the mapping of a systolic circuit to a linear array of FPGAs (see figure 2). If allowed to map freely, the algorithm will map in a certain manner (the up arrows), or the mirror image around the horizontal (the down arrow). Since the individual FPGAs are mapped independently, some will choose one orientation, while others will choose the other. The problem is that there is a good chance that one of the unmapped FPGAs will be left with some neighbors in one orientation, and others in the other orientation (FPGA D). These FPGAs will have their mapping task complicated by the pin assignment imposed on them by their neighbors.

Figure 3. Checkerboard (left) and wavefront (right) pin assignment placement orders.

There is an alternative approach to the checkerboard algorithm, which trades longer mapping run times for better results. The idea is to make sure that FPGAs are not mapped completely independently from each other. In the first

step, a single FPGA is placed. The FPGA that is most constrained by the system's architecture (i.e. by special global signals or external interface connections) is normally chosen, since they should benefit most from avoiding extra pin constraints. In succeeding steps, neighbors of previously placed FPGAs are chosen to be placed next, with as many FPGAs placed as possible without simultaneously placing interconnected FPGAs. For example, in a 4-way mesh, where the first FPGA routed is in the upper-left corner, the mapping process would proceed in a diagonal wave from upper-left to lower-right. In this way, mappings "grow" from a single "seed" assignment, and will be more related to one another than in the checkerboard approach, hopefully easing the mapping tasks for all of the FPGAs.

Unfortunately, even this "wavefront" placement order may not generate good pin assignments. Most obviously, while the individual FPGA placements attempt to find local optimums, global concerns are largely ignored. For example, while pairs of signals that are used together in an FPGA will be placed together in the mapping, the fact that two of these pairs are used together in a neighbor will not be discovered, and these pairs may be assigned pin locations very distant from each other.

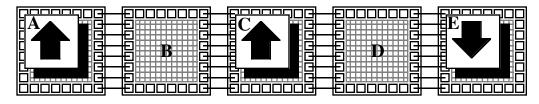

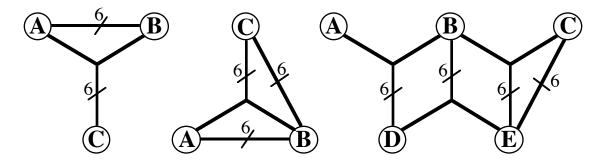

**Figure 4.** Examples of FPGA topologies that cannot be handled by sequential placement pin assignment techniques. Each of these topologies can be found as subcomponents in current systems, with all of these occuring in [Lewis93], and all but the topology at right in both [Bertin93, Thomae91].

Even worse than the speed and quality problems of both the checkerboard and wavefront methods (hereafter referred to jointly as "sequential placement methods") is the fact that there are some topologies that cannot be handled by these methods. Specifically, when the wires that connect FPGA pins are allowed to connect more than two FPGAs there is the potential for conflicts to arise, conflicts that can cause assignment failures with sequential placement methods. For example, consider the topology in figure 4 left. Assume that the logic we wish to map to this topology has one connection between A and C, one between B and C, and six between A and B (Note that while this and other examples in this paragraph are specifically crafted to best show the underlying problems, each of these specific examples represent more general situations, and most wire and mapping connection counts can be changed without fixing these problems). Since all three FPGAs in this topology are directly connected, both the wavefront and checkerboard approach would place these FPGAs sequentially. If FPGA A is placed first, it could assign five of its connections to B, as well as its single connection to C, on the three-destination wires connecting A, B, and C. This means that there is no longer any way to route the connection between B and C, and the assignment fails. The same

thing can happen when FPGA B is placed first. In the specific case of the topology at left, we could place FPGA C first, and avoid the conflicts described previously. Unfortunately, topologies such as that in figure 4 center have no order that is guaranteed to work. Assume that for this topology we wish to map a circuit with one connection between A and C, seven between A and B, and seven between B and C. In this situation at least one connection between each pair of FPGAs must be placed on a three-destination wire. However, regardless of the order, the first FPGA placed can use all of the three-destination wires for its own signals, causing the assignment to fail.

Instead of trying to find a placement order that will work, we could instead try to restrict the choices available to the placement tools. For example, in the mapping to the topology in figure 4 center we know that each FPGA pair must have at least one connection assigned to the three-terminal wires. We could ensure that the placement tool generates a successful mapping by reserving wires for these signals. That is, if we placed FPGA B first, one of the three-destination wires would be reserved for a connection between A and C by disallowing the placement of signals from B onto the corresponding pin location. However, not only is this decision arbitrary, generating lower quality mappings since we have no method to pick a good wire to reserve, but it can also require significant effort to determine which and how many wires to reserve. For example, in the topology in figure 4 right, a connection between B and E could be assigned either to a three-terminal wire also connected to D, or a wire also connected to C. If we do nothing to reserve space for it, connections between other FPGAs can fill these wires, making the assignment fail. We cannot reserve space on both wires, since all the capacity in the system may be required to successfully handle the mapping. However, to determine which wire to reserve requires the system to examine not only FPGA B's and E's connections, but also D's, C's, and A's connections, since congestion on one wire can ripple through to the wires between B and E. Thus, determining the wires to reserve for one FPGA's connections can involve examining most or all FPGAs in the system. Note that while some of these topologies may seem contrived, topologies similar to that in figure 4 center are fairly common, and arise when a local interconnect is augmented with global connections, connections that include adjoining FPGAs.

### Force-Directed Pin Assignment For Multi-FPGA Systems

As we have shown, pin assignment via sequential placement of individual FPGAs can be slow, cannot optimize globally, and may not work at all for some topologies. What is necessary is a more global approach which optimizes the entire mapping, while avoiding sequentializing the placement step. In the rest of this paper we will present one such approach, and then give a quantitative comparison with the approaches presented earlier.

Intuitively, the best approach to pin assignment would be to simultaneously place all FPGAs, with the individual placement runs communicating with each other to balance the pin assignment demands of each FPGA. In this way a global optimum could be reached, and the mapping of all FPGAs would be completed as quickly as any single placement could be accomplished. Unfortunately, tools to do this do not exist, and the communication necessary to perform this task could become prohibitive. Our approach is similar to simultaneous placement, but we will perform the assignment on a single machine within a single process. Obviously, with the placement of a single

FPGA consuming considerable CPU time, complete placement of all FPGAs simultaneously on a single processor is impractical, and thus simplification of the problem will be key to a workable solution.

Our approach is to use force-directed placement of the individual FPGAs[Shahookar91]. In force-directed placement, the signals that connect logic in a mapping are replaced by springs between the signal's source and each sink, and the placement process consists of seeking a minimum net force placement of the logic ("net force" indicates that forces in opposite directions cancel each other. Note that the spring force is calculated based on the Manhattan distance). By finding this minimum net force configuration, we expect to minimize wirelength in the resulting mapping. To find this configuration, the software randomly chooses a logic block and moves it to its minimum net force location. This hill-climbing process continues until a local optimum is found, at which point the software accepts the current configuration.

Force-directed placement may seem a poor choice for pin assignment, and is generally felt to be inferior to simulated annealing for FPGA placement. Two reasons for this are the difficulty force-directed placement has with optimizing for goals other than wirelength, and the inaccuracy of the spring approximation to routing costs. However, as we will see, force-directed placement can handle all of the optimization tasks involved in pin assignment, and the spring metric is the key to efficient handling of multi-FPGA systems.

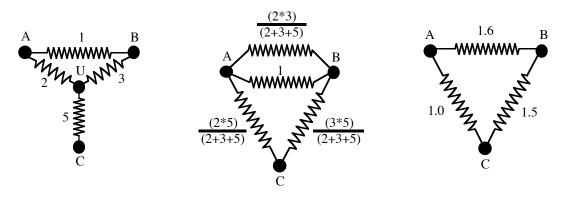

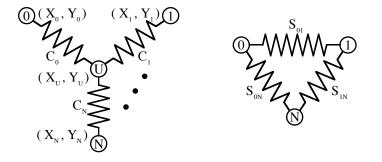

**Figure 5.** Example of spring simplification rules. Source circuit at left has node U replaced at center, and any springs created in parallel with others are merged at right.

As implied earlier, we will not simply place individual FPGAs, but will in fact use force-directed placement simultaneously on all FPGAs in the system. We make two alterations to the basic force-directed algorithm: First, we do not restrict logic blocks to non-shared, discrete locations, but instead allow them to be freely placed into any location in the FPGA with no regard to congestion or physical logic block boundaries (However, mapping I/O pins ARE constrained to exact pin locations, and mapping I/Os cannot share a single pin location). Second, between moves of I/O pins we assume that all logic blocks are moved to their optimal positions. While the second alteration is simply a change in the movement order of nodes, the first change could cause a significant loss in accuracy. However, the resulting degradation of the local optimum will turn out to be more than made up for by the ability to seek the global optimum. Also, while this assumption allows logic blocks to share physical locations, something

that cannot be done in valid FPGA mappings, our force-directed placement is only to determine I/O pin assignments, and the logic blocks will be placed in a later step by standard FPGA placement tools.

By making the two assumptions just given, we now have the opportunity to greatly simplify the mapping process. Specifically, since we are only performing pin assignment, we do not care where the individual logic blocks are placed. Thus, we can examine the system of springs built for the circuit mapping, and use the laws of physics to remove nodes corresponding to FPGA logic blocks, leaving only I/O pins. As shown in appendix A, as well as in the example of figure 5, the springs connected between an internal logic node and its neighbors can be replaced with a set of springs connected between the node's neighbors while maintaining the exact same forces on the other nodes. By repeatedly applying these simplification rules to the logic nodes in the system, we end up with a mapping consisting only of I/O pins, with spring connections that act identically to the complete mapping they replace. In this way, we simplify the problem enough to allow the pin assignment of a large system of FPGAs to be performed efficiently. Note that this spring replacement process can take a significant portion of the algorithm's run-time, primarily because the replacement time is dependent upon the number of springs connected to the node being removed, and the replacement of a node causes all of its neighbors to become connected. This effect can be mostly alleviated by replacing nodes in increasing order of the number of springs connected to that node.

There are some details of the force-directed algorithm that need to be considered here. First of all, there are two ways to perform individual node moves in the algorithm. A simple approach is to pick a node and swap it with whichever node yields the least overall net force. A more complex approach is to perform a ripple move, where a node is moved to its optimum location, and any node occupying this location is then moved. This continues until the destination of the current node to move is empty, at which point the move as a whole is evaluated. If it is a beneficial move it is accepted, if not it is rejected. Note that during this process the nodes already moved are flagged, and are not allowed to move again until a complete ripple move is over. While it is tempting to go with the simplicity of the swap move, there are some topologies for which swap moves yield poor results. Specifically, consider an FPGA with a total of 3 three-terminal wires, one to A and B, one to B and C, and one to A and C. Now consider a mapping onto this structure with a separate connection to each of the neighbor FPGAs. In this situation it is impossible to make a correct swap move, since no two connections have the same two wires as possible assignments.

Another issue with the algorithm has to do with the starting position. While we would like to construct an initial, correct assignment for each wire, this can be very complex. As we indicated in the discussion of the topology in figure 4 right, determining onto which wire a signal can be placed can require the examination of most or all connections in the system. An easier answer is to start with all wires unassigned, and always accept all valid ripple moves that start with an unassigned connection. In this way the mechanisms already required to perform moves of previously assigned pins can be easily extended to handle unassigned pins as well.

$$\sum_{i=1}^{n} SpringConst_{i} \times (pos_{i} - pos_{node}) = \left(\sum_{i=1}^{n} SpringConst_{i} \times pos_{i}\right) - \left(\sum_{i=1}^{n} SpringConst_{i}\right) \times pos_{node}$$

(1)

Efficiency in the calculation of the individual moves is another important problem. To determine the best possible destination of a node during a ripple move it is necessary to calculate the net force for each wire that connects the FPGAs the signal moves between. This is necessary because there is not necessarily any relationship between the location of an I/O pin on one FPGA and the location of the pin the wire goes to on another FPGA (in fact, there is some advantage to be gained by scattering pin connections [Hauck94]). Because of this, it is unlikely that there would be any method for pruning the search space of possible move destinations. This can be very troubling, especially because the node replacement method described above causes nodes to be connected to most or all other nodes in the same FPGA. However, as shown in equation 1, the standard force equation (at left) can be reformulated so that the information from all springs connected to a node can be combined at the beginning of a move, and the calculation of the net force at each location requires only a small amount of computation. Another method for speeding up the process is to remember what connections have been starting points of ripple moves that were determined not to be beneficial, and thus not moved. Then, the algorithm will not try these moves again until another pin on that connection's FPGAs has been successfully moved.

A final extension necessary is software support to help avoid the problems found in the sequential approaches described above. Just as the topologies in figure 4 caused problems for the other approaches, they could cause difficulties with the force-directed approach. Imagine that we have the topology in figure 4 left, and there are six connections between A and C, and one connection between A and B. At some point, all the three-destination wires will be occupied by connections between A and C. If we begin a ripple move with the connection between A and B, its best position might be on one of the three-destination wires. Unfortunately, while these wires must be occupied by the connections between A and C, and cannot accept the connection between A and B, this fact will not be determined until 5 of the 6 connections between A and C have been moved as part of this ripple move. At that point all of the wires will have connections assigned to them which have been flagged as part of the current ripple move, and the final connection between A and C will have no allowable assignment. While we can undo the ripple move, there is no way to tell the connection from A to B that it needs to try one of the two-terminal wires.

Our solution to the problems with the topologies in figure 4 is to add the notion of equivalence classes to the system. That is, every wire in the system is a member of exactly one equivalence class, and each class contains only those wires that connect exactly the same FPGAs. For example, the topology in figure 4 center would have three equivalence classes, one for the two-terminal wires between A and B, another for the two-terminal wires between B and C, and a final class for the three-terminal wires connecting A, B, and C. For each equivalence class we maintain a count of the number of wires within the equivalence class that have no connection assigned to them. Then, whenever a connection wishes to be assigned to a wire in an equivalence class, it can only do so if either the equivalence class has an unassigned wire, or if one of the (unflagged) connections already assigned to the class can be

moved to another equivalence class (moving this connection to another class requires the same check to be performed on that class). Note that much of this information can be cached for greater efficiency, since if at one point in a ripple move an equivalence class cannot accept a connection, it cannot accept a connection at any future point during that move. Thus, in the previous example where it took several moves to determine that the connection between A and B shouldn't be moved onto a three-terminal wire in figure 4 left, this fact would be immediately apparent from the equivalence classes. This would allow the search for possible moves to be pruned, and the connection would be forced to move to one of the two-terminal wires between A and B, the only legal assignments for that connection.

As mentioned earlier, our force-directed approach is capable of handling most of the optimization issues necessary for pin assignment. First of all, since very little detail of the individual FPGAs is necessary beyond the location of the I/O pins, it is very easy to port this software to different FPGAs. In fact, our current system allows different FPGA architectures and sizes to be intermingled within a single multi-FPGA system. We can also accommodate crossbar chips, chips where minimizing wirelength is unnecessary, by setting the spring constant of all springs within such chips to zero. The assignments of mapping I/Os to pins going to the crossbar can also be removed after pin assignment is complete. In this way, connections that require pin assignment can be assigned by our tool, while connections to the crossbar can be left unconstrained. Altering spring constants can also be important for delay optimization. Although our tool currently does not optimize critical paths, and assigns a spring constant of one to all non-crossbar springs, the tool could easily be extended to increase the spring constant on critical paths. This would cause critical path I/Os to be clustered closer together at the chip edge, improving performance. Another important consideration is support for predefined pin assignments for some special connections. Specifically, special connections such as clocks, reset signals, fixed global communication lines, and host interfaces need to be assigned to specific pin locations. Handling these constraints in the pin assignment tool is trivial, since the support necessary to flag nodes that participate in the current ripple move can be extended to permanently freeze a connection in a specified position. Note also that any special chip features in an FPGA, such as the source of global distribution lines, can be handled similarly by defining a special pin location at the special feature site, and always preassigning the feature node to that point. For signals within FPGAs that are globally distributed via special resources, resources that make wirelength minimization irrelevant, the corresponding springs can simply be removed, or have their spring constants set to zero. Finally, there are other limited resources within an FPGA that might require special processing. For example, in Xilinx FPGAs [Xilinx93] there are a limited number of horizontal longlines which can be used as wide multiplexors or wired ANDs. To handle these features, the corresponding nodes in the circuit graph could be left unremoved, and force-directed placement could be applied to these elements as well (though these resources would of course require different potential positions than the pin locations). By doing this, a more accurate assignment could be performed without greatly affecting runtimes. Also, for the specific case of the Xilinx longlines, where the horizontal portion of the Manhattan distance is unimportant (the longlines stretch the width of the chip), these nodes could be specially marked, and the force calculation could be set up to properly ignore the horizontal component.

| System     |          | Splash   |          | DECPeR   | Le-1     | Virtual V | Vires    | Marc-1    |          |

|------------|----------|----------|----------|----------|----------|-----------|----------|-----------|----------|

| Mapping    |          | DNA Con  | parator  | Calorime | ter      | Palindror | ne       | Logic Sin | 1.       |

|            |          |          |          |          |          |           |          | Processor |          |

| Force -    | Time     | 34:25    |          | 29:14    |          | 13:18     |          | 26:36     |          |

|            | Uniproc. | 12:05:12 |          | 2:43:18  |          | 1:44:37   |          | 3:38:11   |          |

|            | Distance | 143690.9 |          | 45159.4  |          | 41255.4   |          | 102728.6  |          |

| Wavefront  | - Time   | 5:35:40  | (9.7530) | 2:11:33  | (4.5000) | 22:01     | (1.6554) | Failure   |          |

|            | Uniproc. | 13:24:58 | (1.1100) | 3:10:02  | (1.1637) | 1:27:34   | (0.8370) |           |          |

|            | Distance | 146424.8 | (1.0190) | 45661.2  | (1.0111) | 41111.8   | (0.9965) |           |          |

| Checkerbrd | - Time   | 1:07:00  | (1.9467) | 1:51:24  | (3.8107) | 13:56     | (1.0476) | Failure   |          |

|            | Uniproc. | 12:37:36 | (1.0447) | 2:55:24  | (1.0741) | 1:28:19   | (0.8442) |           |          |

|            | Distance | 149860.5 | (1.0429) | 46522.5  | (1.0302) | 41900.7   | (1.0156) |           |          |

| Random -   | Time     | 1:00:18  | (1.7521) | 30:47    | (1.0530) | 10:37     | (0.7982) | 26:38     | (1.0013) |

|            | Uniproc. | 17:45:56 | (1.4698) | 2:56:44  | (1.0823) | 1:28:35   | (0.8467) | 4:36:32   | (1.2674) |

|            | Distance | 156038.2 | (1.0859) | 48713.4  | (1.0787) | 42225.3   | (1.0235) | 108236.1  | (1.0536) |

Table 1. Quantitative comparison table. Numbers in parentheses are normalized to the force-directed algorithm's results.

# **Comparison of Pin Assignment Approaches**

In order to get a feeling for how good the various pin assignment approaches are, we tested each approach on mappings for four different current systems. These include a systolic DNA comparison circuit for SPLASH [Lopresti91], a calorimeter circuit for DECPeRLe-1 [Bertin93], a palindrome circuit for the Virtual Wires Emulation system [Tessier94], and a RISC processor configured for logic simulation on the Marc-1 system [Lewis93]. The pin assignment systems compared are "random", which randomly assigns connections to wires, "checkerboard" and "wavefront", which use sequential placement runs to do pin assignment, and "force", which uses the force-directed pin assignment technique described above. The results include both mapping time and resulting wirelength. The time is CPU time on a SPARC-10, and includes the time to perform pin assignment as well as individual FPGA place and route, and assumes enough machines are available to achieve maximum parallelism. Uniprocessor time,

the time it takes to complete all of these tasks on a single machine, is also included. Note that the sequential placement techniques only sequentialize the placement step, while routing is allowed to be performed in parallel with subsequent placements and routings. These placement attempts are begun as soon as possible, so that for example in the checkerboard algorithm, we do not need to wait to begin placing FPGAs of one color until all FPGAs of the previous color are placed, but instead can proceed with a placement once all of its neighbors in the previous color(s) have been completed. Also, the random approach is assumed to be able to generate a pin assignment in zero time, so its time value is simply the longest time to place and route any one of the individual FPGAs. The wirelength is determined by summing up all source to sink delays for all signal routes in the FPGAs. While this is not exact, since some portions of a multi-destination signal route will be included more than once, it gives a reasonable approximation of the routing resource usage of the different systems.

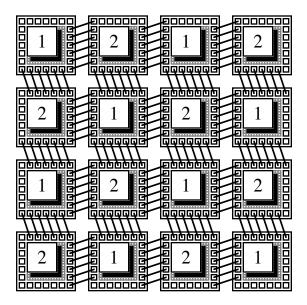

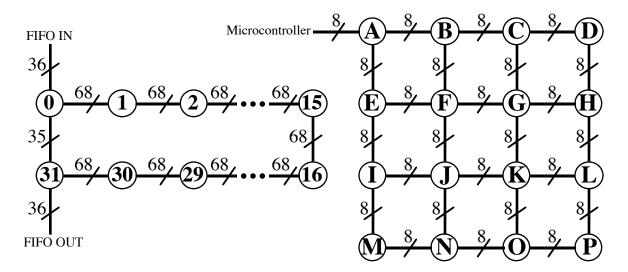

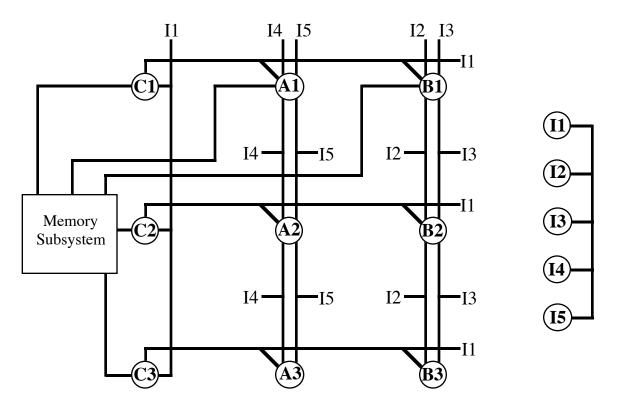

**Figure 6.** The Splash (left) and Virtual Wires (right) topologies. Note that system features not used in the example mappings, as well as global communication wires and clocks, are omitted.

The Splash system [Lopresti91] is a linear array of Xilinx 3090 FPGAs, with memories attached to some of the communication wires. As expected, Random does poorly on the average wirelength, with Checkerboard and Wavefront each doing successively better. However, the Force-Directed approach does the best, since it is able to optimize the mapping globally. More surprising is the fact that the Force-Directed approach is actually faster than all the other approaches, including the Random approach, in both parallel and uniprocessor times. The reason for this is that the poor pin assignment generated by the random approach significantly increases the routing time for some of its FPGAs, up to a factor of more than 4 times as long. Note that the time to perform the force-directed pin assignment does not dominate for either this or any other mapping. For the DNA mapping it is only 9% of the overall runtime, for Palindrome it is 6%, and for Calorimeter it is 8%, though for the Marc-1 mapping it is 31%. The results are almost identical for the DECPeRLe-1 board [Bertin93], a four by four Mesh of Xilinx 3090 FPGAs with seven additional support FPGAs. However, the Checkerboard approach takes much longer on the DECPeRLe-1

board than it did on the Splash board, making it only about 15% faster than the Wavefront approach. The reason is that the DECPeRLe-1 board, which has 23 FPGAs, is only 19-colorable, leaving very little parallelism for the Checkerboard algorithm to exploit.

The Virtual Wires board [Tessier94] is a 4-directional Mesh of Xilinx 4005 FPGAs, with the connections in a given direction scattered around the FPGA's edge. The results for this mapping are less favorable than for the DNA comparator and the calorimeter, with the Wavefront method actually generating a slightly better assignment than the Force-Directed approach. However, we believe the reason for this poor performance is the special techniques applied to the mapping prior to pin assignment. The Virtual Wires system [Babb93] attempts to overcome FPGA I/O limitations by time-division multiplexing the chip outputs. Thus, each chip I/O is connected to a shift chain, which is connected to the actual I/O signals of the mapping. Unfortunately, the choice of which wires to combine is done arbitrarily, without regard to the mapping structure. Thus, instead of combining signals that are close together in the logic, signals from very distant portions of an FPGA's mapping may be merged. Because of this, there is very little structure left in the mapping, and there is little pin assignment can do to improve things. We believe that a more intelligent combining strategy, possibly driven by the spring constants generated by our spring simplification approach, would generate better mappings, mappings that can also be helped by good pin assignments.

**Figure 7.** Schematic of the Marc-1 board. The entire board consists of two copies of the subsystem at left, and one copy of the subsystem at right. Labels without circles indicate connections to the corresponding FPGA circle. Note that system features not used in the example mappings, as well as global communication wires and clocks, are omitted.

The Marc-1 board [Lewis93] is a complex system of Xilinx 4005 FPGAs, as shown in figure 7. As mentioned earlier, this board includes all topologies from figure 4, topologies that make mapping failures possible in sequential placement approaches regardless of placement order. We attempted to use these sequential approaches four times each on this system, but each time it failed because of resource conflicts (note that even had they succeeded, the topology is only 5-colorable, and the Wavefront method would sequentialize 9 placement runs, which in both cases would greatly increase runtimes). However, our force-directed approach easily handled this topology, and generated a good assignment. Note that while the force-directed result is somewhat less of an improvement than the DNA comparator led us to expect, this may be due to the fact that only 51% of the logic pins are assignable, with the others fixed by memory interfaces and other fixed global signals.

### **Conclusions and Future Work**

As we have shown in this paper, pin assignment for FPGA arrays is a difficult problem that has not been previously studied. We presented some approaches for using existing tools, as well as a new force-directed algorithm that can help improve mapping quality. The force-directed approach is almost always faster than all other approaches, up to a factor of ten, and almost always delivers superior routing resource usage, up to an 8.6% decrease in total resource usage in the entire system.

Several possible extensions have been mentioned earlier for improving mapping quality, and these are worth further study. More importantly, the spring cost metric is not necessarily tied to force-directed placement, but could instead be used within a simulated annealing algorithm. While we believe simulated annealing would not yield significant improvements, since the cost metric is so abstracted from the real situation, and since simulated annealing is so time-consuming, a study of it's actual benefits should be performed. Another interesting change is to explore subdividing large systems into smaller parts, and perform force-directed pin assignments only on these subsystems. With the proper overlapping of subsystems such that a subsystem has enough information on its neighbors to find a reasonable assignment, and with orderings of subsystem force-directed placement similar to the checkerboard algorithm, substantial time savings might be achieved for larger mappings. Also interesting is the approach mentioned above for improving Virtual Wires mappings by guiding wire combining by the spring forces our system generates. We hope that such an approach would not only improve the overall placements achieved by Virtual Wires, but also show the benefits of good pin assignments in this domain.

### Acknowledgments

This paper has benefited greatly from the patience and support of many people, including Patrice Bertin, Duncan Buell, David Lewis, Daniel Lopresti, Brian Schott, Mark Shand, Russ Tessier, Herve Touati, and Daniel Wong. This research was funded in part by the Defense Advanced Research Projects Agency under Contract N00014-J-91-4041. Gaetano Borriello was supported in part by an NSF Presidential Young Investigator Award, and Scott Hauck was supported by an AT&T Fellowship.

# References

- J. M. Arnold, "The Splash 2 Software Environment", *IEEE Workshop on FPGAs for Custom Computing Machines*, pp. 88-93, 1993.

- J. Babb, R. Tessier, A. Agarwal, "Virtual Wires: Overcoming Pin Limitations in FPGA-based Logic Emulators", *IEEE Workshop on FPGAs for Custom Computing Machines*, pp. 142-151, 1993.

- P. Bertin, D. Roncin, J. Vuillemin, "Programmable Active Memories: a Performance Assessment", *Research on Integrated Systems: Proceedings of the 1993 Symposium*, pp.88-102, 1993.

- P. K. Chan, M. D. F. Schlag, "Architectural Tradeoffs in Field-Programmable-Device-Based Computing Systems", IEEE Workshop on FPGAs for Custom Computing Machines, pp. 152-161, 1993.

- P. K. Chan, M. Schlag, M. Martin, "BORG: A Reconfigurable Prototyping Board Using Field-Programmable Gate Arrays", *Proceedings of the 1st International ACM/SIGDA Workshop on Field-Programmable Gate Arrays*, pp. 47-51, 1992.

- S. Hauck, G. Borriello, C. Ebeling, "Mesh Routing Topologies for FPGA Arrays", FPGA '94, Berkeley, 1994.

- D. M. Lewis, M. H. van Ierssel, D. H. Wong, "A Field Programmable Accelerator for Compiled-Code Applications", ICCD '93, pp. 491-496, 1993.

- D. P. Lopresti, "Rapid Implementation of a Genetic Sequence Comparator Using Field-Programmable Logic Arrays", Advanced Research in VLSI 1991: Santa Cruz, pp. 139-152, 1991.

- K. Shahookar, P. Mazumder, "VLSI Cell Placement Techniques", ACM Computing Surveys, Vol. 23, No. 2, pp. 145-220, June 1991.

- R. Tessier, J. Babb, M. Dahl, S. Hanono, A. Agarwal, "The Virtual Wire Emulation System: A Gate-Efficient ASIC Prototyping Environment", FPGA '94, Berkeley, 1994.

- D. A. Thomae, T. A. Petersen, D. E. Van den Bout, "The Anyboard Rapid Prototyping Environment", Advanced Research in VLSI 1991: Santa Cruz, pp. 356-370, 1991.

- J. Varghese, M. Butts, J. Batcheller, "An Efficient Logic Emulation System", *IEEE Transactions on VLSI Systems*, Vol. 1, No. 2, pp. 171-174, June 1993.

- M. Wazlowski, L. Agarwal, T. Lee, A. Smith, E. Lam, P. Athanas, H. Silverman, S. Ghosh, "PRISM-II Compiler and Architecture", *IEEE Workshop on FPGAs for Custom Computing Machines*, pp. 9-16, 1993.

- Xilinx Development System Reference Guide and The Programmable Logic Data Book, Xilinx, Inc., San Jose, CA, 1993.

## **Appendix A: Spring Replacement Rules**

As discussed earlier, we wish to reduce the complexity of the force-directed placement algorithm by replacing all springs touching non-IO nodes with equivalent springs only involving IO nodes. To do this, we iteratively remove

individual internal nodes from the system, and replace the attached springs with new springs between the removed node's neighbors.

Since we are using a Manhattan distance metric, the forces along the X and Y dimension are independent, and are given in equation A1.

$$F_x = C \times (X_1 - X_2)$$

$F_y = C \times (Y_1 - Y_2)$  (A1)

C is the spring constant, and  $(X_1, Y_1)$  and  $(X_2, Y_2)$  are the locations of the nodes connected by the spring. There are two simplification rules necessary for our purposes: parallel spring combining, and node removal. For parallel springs, springs which connect the same two endpoints, the springs can be merged into a single spring whose spring constant is the sum of the parallel springs.

Figure A1. Spring system before node U is removed (left) and after (right).

In node removal, we wish to remove an internal node, and replace the springs connected to that node with equivalent springs connected between the node's neighbors. As shown in figure A1, we have the node U with N+1 neighbors labeled 0..N (note that if node U has only one neighbor, the node and the spring can simply be removed, since it will never exert force on its neighbor). Node i is located at  $(X_i, Y_i)$ , and is connected to node U by a spring with spring constant C<sub>i</sub>. As discussed earlier, we assume that internal nodes are always placed at their optimal location, which is the point where the net force on the node is zero. Thus, we can calculate the location of node U as shown in equations A2 and A3 (note that from now on we will work with only the X coordinates of all nodes. Similar derivations can be found for the Y coordinates as well).

$$0 = \sum_{i=0}^{n} C_i \times (X_i - X_U) = \left(\sum_{i=0}^{n} C_i \times X_i\right) - X_U \times \sum_{j=0}^{n} C_j$$

(A2)

$$X_U = \frac{\sum_{i=0}^n C_i \times X_i}{\sum_{j=0}^n C_j}$$

(A3)

To replace the springs connected to node U, we must make sure the new springs provide the same force as the old springs. So, we start with the force equation from A1, and substitute in the location found in A3. The results are equations A4-A7

$$F_{k} = C_{k} \times (X_{U} - X_{k}) = \frac{C_{k} \times \left(\sum_{i=0}^{n} C_{i} \times X_{i}\right)}{\sum_{j=0}^{n} C_{j}} - C_{k} \times X_{k} \quad (\mathbf{A4}) \qquad F_{k} = \frac{C_{k} \times \left(\sum_{i=0}^{n} C_{i} \times X_{i}\right) - C_{k} \times X_{k} \times \sum_{l=0}^{n} C_{l}}{\sum_{j=0}^{n} C_{j}} \quad (\mathbf{A5})$$

$$F_{k} = \frac{\left(\sum_{i=0}^{n} C_{k} \times C_{i} \times X_{i}\right) - \left(\sum_{l=0}^{n} C_{k} \times C_{l} \times X_{k}\right)}{\sum_{j=0}^{n} C_{j}} \quad (\mathbf{A6}) \qquad F_{k} = \sum_{i=0}^{n} \left(\frac{C_{k} \times C_{i}}{\sum_{j=0}^{n} C_{j}} \times (X_{i} - X_{k})\right) \quad (\mathbf{A7})$$

From A6 it is now clear how to replace the springs incident on node U. We can replace all of these springs, and insert a new spring between each pair of neighbors of node U. The new spring between nodes J and K will have a spring constant  $S_{jk}$  as given in equation A8.

$$S_{jk} = \frac{C_j \times C_k}{\sum\limits_{i=0}^{n} C_i}$$

(A8)