# Architectural Support for Compiler-Generated Data-Parallel Programs

by

Alexander C. Klaiber

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

1994

Approved by\_\_\_\_\_

(Chairperson of Supervisory Committee)

Program Authorized

to Offer Degree\_\_\_\_\_

Date\_\_\_\_\_

In presenting this dissertation in partial fulfillment of the requirements for the Doctoral degree at the University of Washington, I agree that the Library shall make its copies freely available for inspection. I further agree that extensive copying of this dissertation is allowable only for scholarly purposes, consistent with "fair use" as prescribed in the U.S. Copyright Law. Requests for copying or reproduction of this dissertation may be referred to University Microfilms, 1490 Eisenhower Place, P.O. Box 975, Ann Arbor, MI 48106, to whom the author has granted "the right to reproduce and sell (a) copies of the manuscript in microform and/or (b) printed copies of the manuscript made from microform."

Signature\_\_\_\_\_

Date\_\_\_\_\_

#### University of Washington

Abstract

### Architectural Support for Compiler-Generated Data-Parallel Programs

by Alexander C. Klaiber

Chairperson of Supervisory Committee: Professor Henry M. Levy Department of Computer Science and Engineering

To fully realize the advantages of parallel processing demands the design of efficient communication mechanisms. Existing communication architectures span a spectrum ranging from message passing to remote-memory access, shared memory and cache-only architectures. These communication architectures are often used (*and designed to be used*) directly by the programmer. However, in the future we can expect more programs to be written in high-level parallel languages and compiled to the specific parallel target; the compiler will hide the details of the underlying hardware from the programmer. The communication architecture should then be designed with the compiler, not the programmer, in mind.

The goal of our work is to improve communication performance for programs that are written in a high-level parallel language and then compiled to a specific communication architecture. To make this task manageable, we focus on the class of *data-parallel languages* and we pick C\* as one representative for our experiments.

We evaluate three competing communication architectures — message-passing, remotememory access and cache-coherent shared-memory — for a set of benchmarks written in  $C^*$  and compiled to the respective architecture. We show that the message-passing model has several inherent advantages for these benchmarks, resulting in less interconnect traffic and less time spent waiting for messages to traverse the interconnect.

On the other hand, the message-passing architecture requires the CPU to perform significantly more work per message than the other architectures. This communication overhead destroys much of the message passing model's advantage.

We propose a *language-oriented* communication architecture that retains the advantages

of the message-passing model, yet (in cooperation with the compiler) significantly reduces the communication overhead. To do so, we first identify a small set of low-level communication and synchronization primitives that are well matched to the needs of C\*. We then design a network interface that is tuned to these primitives and describe the C\* compilation for this base; our network interface includes hardware for remote read/write requests plus counter-based synchronization support. We simulate and measure our compiled C\* benchmarks on a traditional message-passing interface as well as our language-oriented design; our measurements demonstrate that our design is effective at reducing communicationrelated CPU overhead.

# **Table of Contents**

| List of F | igures  |                                           | iv |

|-----------|---------|-------------------------------------------|----|

| Chapter   | 1:      | Introduction                              | 1  |

| 1.1       | Goal of | f this Dissertation                       | 2  |

| 1.2       | Related | d Work                                    | 3  |

| 1.3       | Contrib | outions of this Dissertation              | 5  |

| 1.4       | Organiz | zation                                    | 6  |

| Chapter   | 2:      | Architectural Framework                   | 7  |

| 2.1       | Process | sing Nodes                                | 7  |

| 2.2       | Interco | nnection Network                          | 9  |

| 2.3       | Networ  | rk Interface                              | 13 |

| 2.4       | Summa   | ary                                       | 15 |

| Chapter   | 3:      | Data-Parallel Languages                   | 17 |

| 3.1       | The C*  | <sup>c</sup> Language                     | 18 |

| 3.2       | C* vers | sus HPF                                   | 21 |

| 3.3       | Summa   | ary                                       | 24 |

| Chapter   | 4:      | The C* Compiler                           | 25 |

| 4.1       | Alterna | ative Communication Models                | 26 |

|           | 4.1.1   | Compiling for a Shared-Memory Target      | 26 |

|           | 4.1.2   | Compiling for a Distributed-Memory Target | 27 |

|           | 4.1.3   | Our Compilation Strategy                  | 30 |

| 4.2       | Compil  | ler Overview                              | 32 |

|           | 4.2.1   | Parallel Computation                      | 33 |

|           | 4.2.2   | Inter-Node Communication                  | 35 |

|           | 4.2.3   | Synchronization                           | 37 |

| 4.3     | Summa    | ury                                          | 39 |

|---------|----------|----------------------------------------------|----|

| Chapter | 5:       | Architectural Comparison                     | 40 |

| 5.1     | Archite  | ctural Models                                | 42 |

| 5.2     | Implem   | nentation of C* Communication Primitives     | 44 |

| 5.3     | Simulat  | tion Methodology                             | 47 |

| 5.4     | Benchn   | narks                                        | 48 |

| 5.5     | Traffic  | Measurements                                 | 49 |

|         | 5.5.1    | Selecting Simulation Parameters              | 49 |

|         | 5.5.2    | Traffic from get and send Operations         | 52 |

|         | 5.5.3    | Traffic from broadcast and reduce Operations | 54 |

|         | 5.5.4    | Synchronization Traffic                      | 57 |

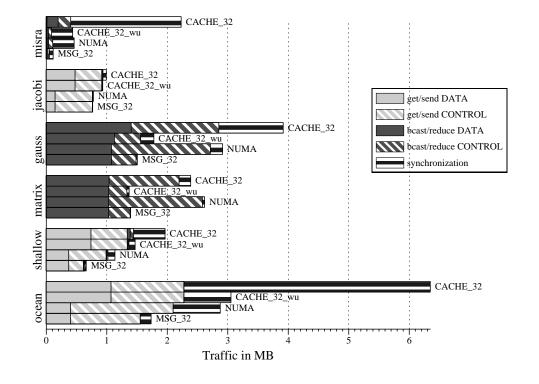

|         | 5.5.5    | Contribution of Traffic Categories           | 58 |

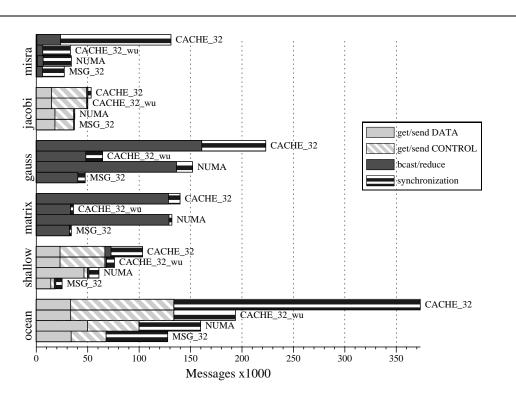

|         | 5.5.6    | Total Number of Messages Sent                | 60 |

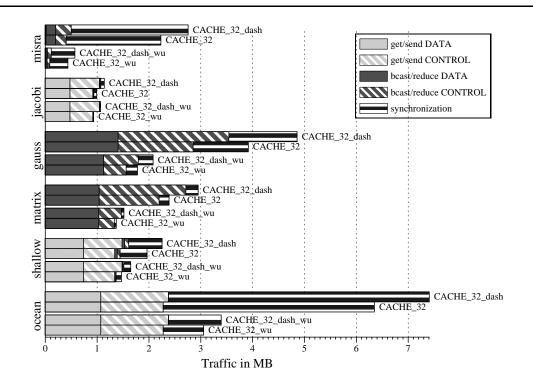

|         | 5.5.7    | Broadcast versus Point-to-Point Interconnect | 61 |

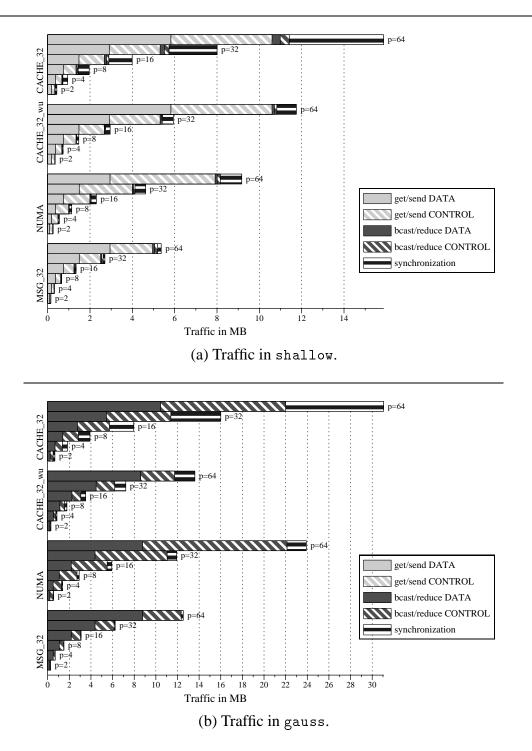

|         | 5.5.8    | Scaling of Benchmarks                        | 63 |

| 5.6     | Latency  | Measurements                                 | 63 |

|         | 5.6.1    | Assumptions and Limitations                  | 66 |

|         | 5.6.2    | Selecting Simulation Parameters              | 68 |

|         | 5.6.3    | Latency in get and send Operations           | 71 |

|         | 5.6.4    | Latency in broadcast and reduce Operations   | 72 |

|         | 5.6.5    | Synchronization Latency                      | 73 |

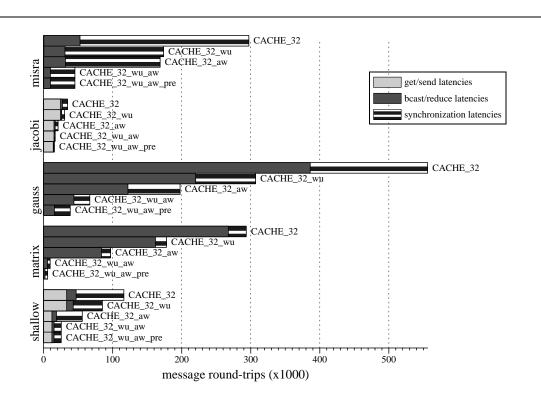

|         | 5.6.6    | Contribution of Traffic Categories           | 74 |

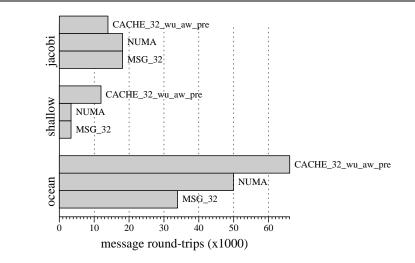

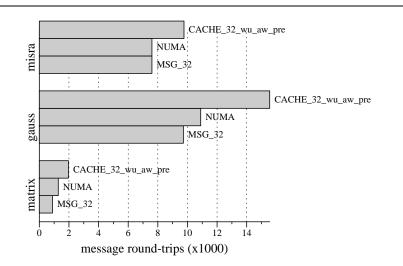

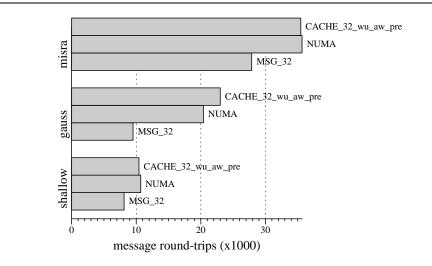

|         | 5.6.7    | Broadcast versus Point-to-Point Interconnect | 75 |

| 5.7     | Related  | l Work                                       | 76 |

| 5.8     | Summa    | ury                                          | 77 |

| Chapter | 6:       | Improving Message-Passing                    | 81 |

| 6.1     | Problem  | ns of Traditional Message Passing            | 82 |

|         | 6.1.1    | Protocol Overhead                            | 82 |

|         | 6.1.2    | NI Management Overhead                       | 83 |

| 6.2     | Traditio | onal Network Interface Design                | 84 |

| 6.3      | New Ne                     | etwork Interface Design               | 88  |

|----------|----------------------------|---------------------------------------|-----|

| 6.4      | 4 Experimental Methodology |                                       |     |

| 6.5      | Results                    |                                       | 95  |

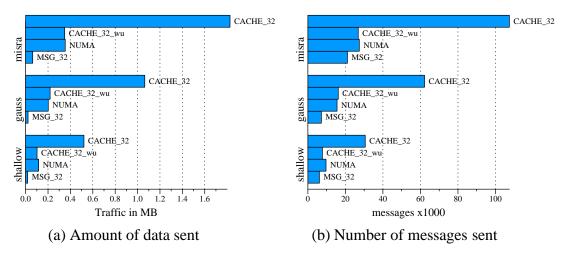

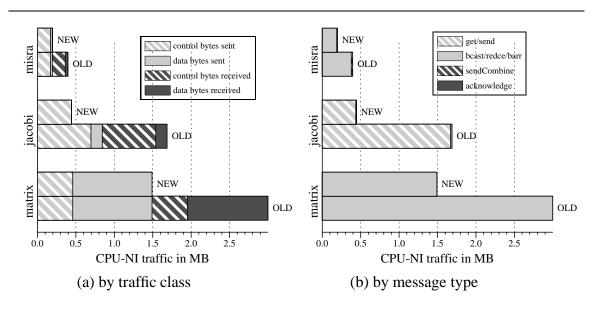

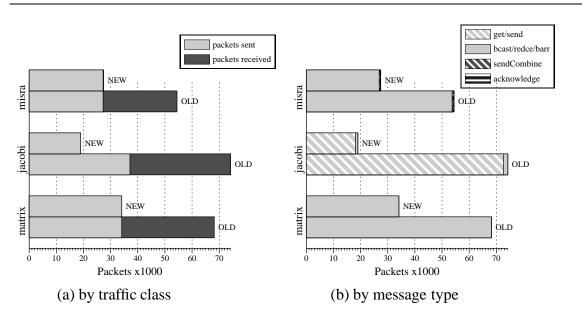

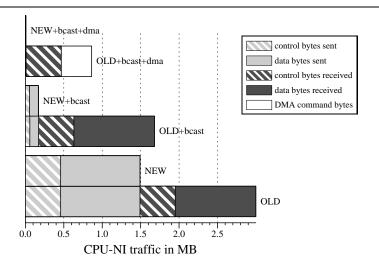

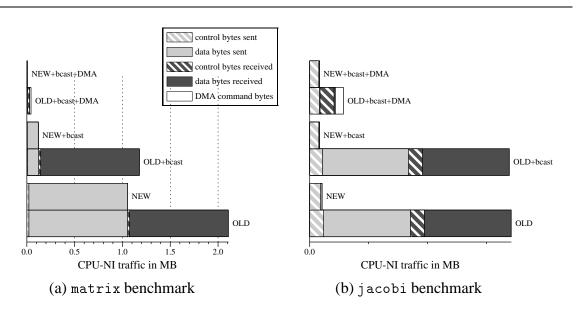

|          | 6.5.1                      | Traffic between CPU and NI            | 95  |

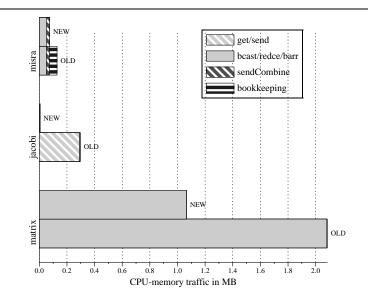

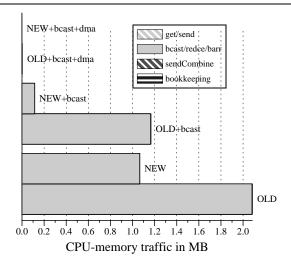

|          | 6.5.2                      | Communication-related Memory Accesses | 96  |

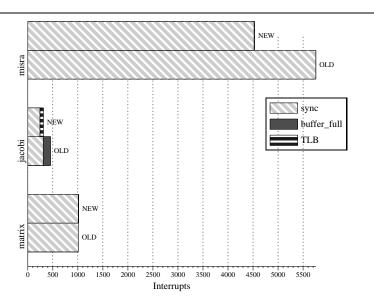

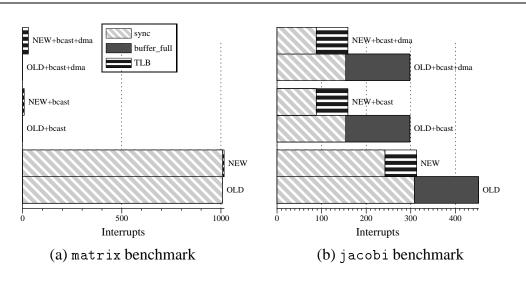

|          | 6.5.3                      | Communication-related Interrupts      | 97  |

|          | 6.5.4                      | Broadcast and DMA Capabilities        | 99  |

|          | 6.5.5                      | Large Packet Sizes                    | 102 |

| 6.6      | Related                    | Work                                  | 103 |

| 6.7      | Summa                      | ry                                    | 105 |

| Chapter  | 7:                         | Conclusions                           | 107 |

| 7.1      | Future V                   | Work                                  | 109 |

|          | 7.1.1                      | Improved Compiler                     | 110 |

|          | 7.1.2                      | Enhancing Shared-Memory Architectures | 110 |

|          | 7.1.3                      | Extending to Wider Class of Programs  | 111 |

| 7.2      | Conclus                    | sions                                 | 111 |

| Bibliogr | aphy                       |                                       | 112 |

# List of Figures

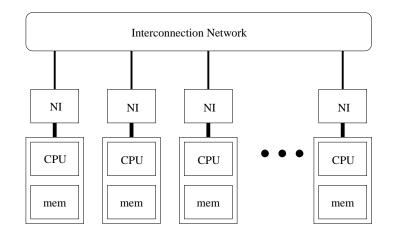

| 2.1  | A generic parallel machine.                                   | 8  |

|------|---------------------------------------------------------------|----|

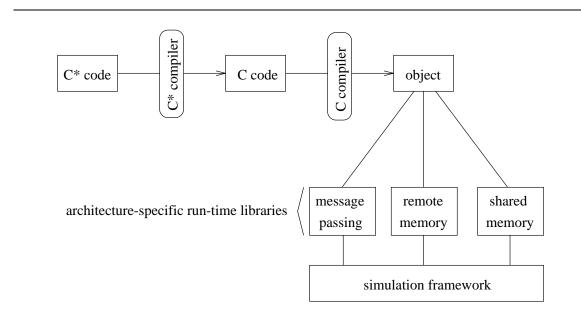

| 4.1  | Compiling C* for multiple target architectures.               | 26 |

| 4.2  | Communication for different communication models.             | 28 |

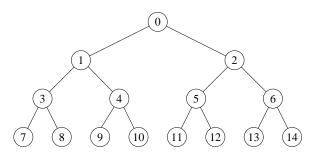

| 4.3  | Fanin/fanout tree of processing nodes.                        | 36 |

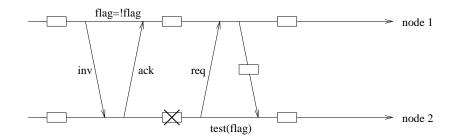

| 4.4  | Preserving inter-node data dependecies.                       | 38 |

| 5.1  | Summary of architectural models.                              | 42 |

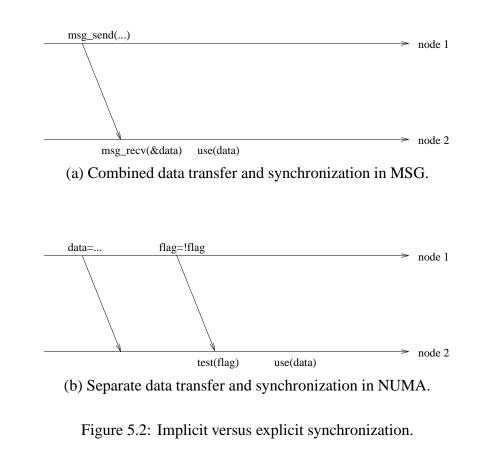

| 5.2  | Implicit versus explicit synchronization.                     | 45 |

| 5.3  | Traffic for synchronization under write-invalidate protocol   | 46 |

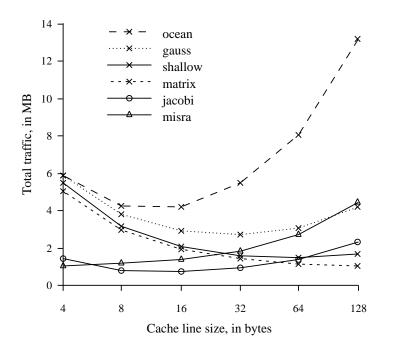

| 5.4  | Total traffic in CACHE model, as function of cache line size. | 50 |

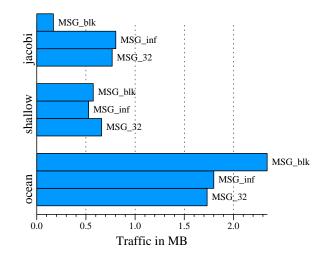

| 5.5  | Message-passing models: total traffic.                        | 51 |

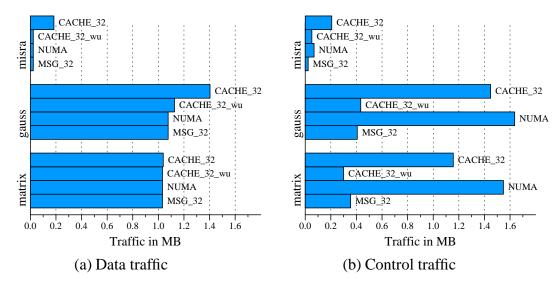

| 5.6  | Comparison of get/send traffic                                | 52 |

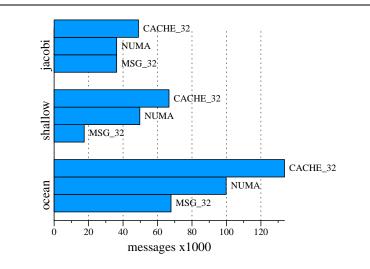

| 5.7  | Number of messages for get/send operations.                   | 53 |

| 5.8  | Comparison of bcast/reduce traffic.                           | 55 |

| 5.9  | Number of messages for bcast/reduce operations.               | 56 |

| 5.10 | Comparison of synchronization traffic.                        | 57 |

| 5.11 | Overall traffic.                                              | 59 |

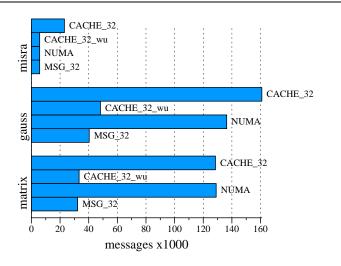

| 5.12 | Overall traffic: number of messages.                          | 60 |

| 5.13 | Traffic in DASH-like and KSR-like models.                     | 62 |

| 5.14 | Traffic as function of number of processors.                  | 64 |

| 5.15 | Summary of models.                                            | 69 |

| 5.16 | Choosing a shared-memory implementation.                      | 70 |

| 5.17 | Communication latency in get and send operations.             | 71 |

| 5.18 | Communication latency in broadcast and reduce operations      | 72 |

| 5.19 | Communication latency for synchronization operations          | 73 |

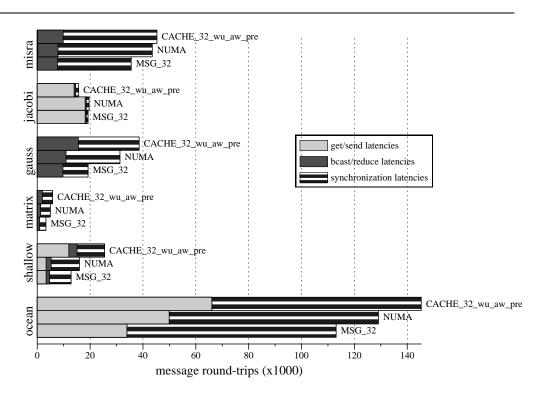

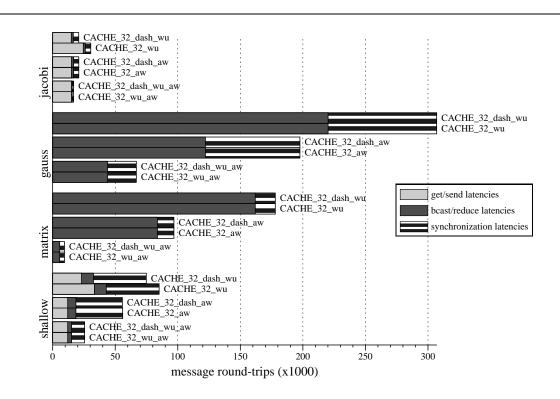

| 5.20 | Contribution of traffic categories.                           | 74 |

| 5.21 | Broadcast versus point-to-point Interconnect.                 | 75 |

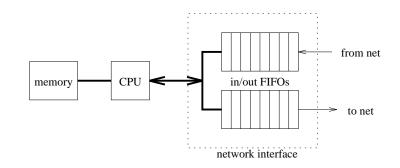

| 6.1  | A generic message-passing network interface                 |

|------|-------------------------------------------------------------|

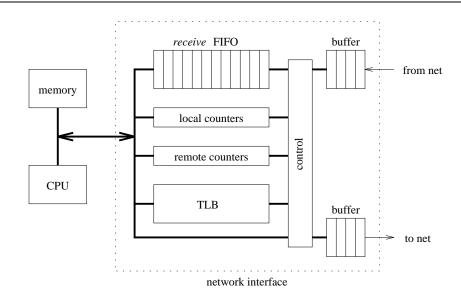

| 6.2  | Language-oriented network interface                         |

| 6.3  | Architectural models evaluated                              |

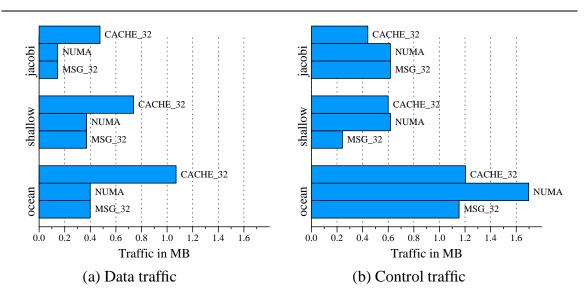

| 6.4  | Total traffic between CPU and NI                            |

| 6.5  | Number of packets sent and received by CPU                  |

| 6.6  | CPU memory accesses by message type                         |

| 6.7  | Number of CPU interrupts, by reason                         |

| 6.8  | CPU-NI traffic with broadcast and DMA, matrix benchmark 100 |

| 6.9  | Memory traffic with broadcast and DMA, matrix benchmark 101 |

| 6.10 | Interrupts with broadcast and DMA                           |

| 6.11 | Total traffic between CPU and NI, large packets             |

# ACKNOWLEDGMENTS

I'd like to thank all the people who have made this possible. My parents for their unwavering support. Beth for keeping me sane. My advisor Hank Levy for teaching me how to do research and, more importantly, how to write. All my fellow grad students for many hours of productive discussions, especially Craig Anderson, Robert Bedichek, Edward Felten, Dave "Pardo" Keppel, Brian Lockyear, Neil McKenzie and Dylan McNamee. Extra thanks to Dylan for his *thorough* reading of the first draft of this dissertation.

Thanks to Jamie Frankel for getting me interested in data-parallel languages in the first place. Phil Hatcher at UNH supplied me with an early version of his compiler for the "new" C\* and most of the benchmarks.

Finally, thanks to Wassif at the Shalimar for keeping me well fed!

To my parents.

# Chapter 1

# INTRODUCTION

Massively parallel computers are an attractive tool for solving many computationally intensive problems. Unlike traditional supercomputers which generally use expensive custom-designed processors, parallel computers can be built from off-the-shelf microprocessors and achieve supercomputer class performance through parallelism. Because of their design, parallel computers gain a significant market advantage by tracking the steady performance improvement of mass-produced commodity parts.

Unfortunately, the cost of *communication* may limit the performance of parallel computers. To fully realize the advantages of parallel processing, we need to design efficient communication mechanisms. Existing *communication architectures* span a spectrum ranging from message passing [Arlauskas 88, Intel 91a, Dally 90, TMC 91b] to remote-memory access [Crowther et al. 85, Cray 93], shared memory [Sequent 87, Lenoski et al. 92, Agarwal et al. 91] and cache-only architectures [Hagersten 92a, KSR 92]. These communication architectures are often used directly by the programmer — a fact that has influenced their design, much as assembly language programming has influenced the design of CISC instruction sets. For example, one commonly cited argument in favor of shared-memory machines is that they are easier to use than message-passing machines — a statement that clearly reveals a design bias towards simplifying the communication architecture for the benefit of the programmer.

However, in the future we can expect more programs to be written in high-level parallel languages and compiled to the specific parallel target; the compiler will hide the details of the underlying communication architecture from the programmer. Hence, the programmer's convenience is no longer a major concern in the design of the communication architecture, since the programming language already provides a convenient programming model. Instead, performance becomes a driving concern, and the communication architecture must provide interfaces that best suit the needs of the compiler. This approach is similar to the RISC philosophy in processor design.

#### 1.1 Goal of this Dissertation

The goal of our work is to improve communication performance for programs that are written in a high-level parallel language and then compiled to a specific communication architecture.

To make this task manageable, we focus on the class of *data-parallel languages*, and we pick the C\* language as one representative for our experiments. The data-parallel model is an important one; a study by Fox [Fox 88] has shown that a majority of existing scientific applications fit that model well. As a framework for our architectural studies, we concentrate on MIMD parallel computers and three competing communication architectures — message-passing, remote-memory access and cache-coherent shared-memory.

The core of this dissertation consists of two parts. In the first part (Chapter 5), we evaluate the three communication architectures in order to gain better insight into their relative strengths, as well as the compiler's demands on the communication architecture. Comparing such widely differing architectures has been difficult in the past, for two reasons. First, applications had to be hand-crafted for each architecture, often resulting in radically different sources for comparison. Second, a host of implementation details (such as processor speed, cache organization and size, and network bandwidth available) can easily obscure any *architecture-inherent* characteristics; given different execution times on different machine configurations, it becomes nearly impossible to attribute the performance differences to any specific source(s).

We avoid these problems by using the following approach. We use a single suite of C\* source programs, compile each program with a C\* compiler, and simulate its execution on the alternative communication architectures. This ensures that the different architectures execute the same source program. Further, our objective is to examine underlying, *implementation-independent* costs inherent in each alternative. To this end, we abstract many implementation details and focus on metrics that are not affected by, say, processor or network speed. For example, we measure the number of messages sent, the total interconnect control and data traffic, and the number of round-trip communication latencies incurred. We deliberately reject overall execution time as a metric, since it cannot yield the same kind of fundamental insight as our implementation-independent metrics. While our results do not directly indicate which architecture is "best," they do show the relative communication work required to execute our data parallel programs on the different architectures. Specifically, we will see that the message-passing model has some inherent

advantages for these benchmarks, resulting in less interconnect traffic and less time spent for messages traversing the interconnect.

In the second part of the dissertation (Chapter 6), we focus specifically on distributedmemory architectures, and we examine one metric that we have ignored in Chapter 5, namely the time to send a message, or the *communication overhead*. We note that in practice, the message-passing communication model incurs significant per-message overhead and thus is unable to fully exploit the advantages we have identified before.

A good communication architecture would combine the advantages of message-passing with the low per-message overhead of shared-memory. As one possible solution, we propose a *language-oriented* design that retains the advantages of the message-passing model, yet (in cooperation with the compiler) significantly reduces the per-message overhead. To do so, we first identify a small set of low-level communication and synchronization primitives that are well matched to the needs of C\* (and, presumably, other data-parallel languages as well). We then design a network interface that is tuned to these primitives and describe the C\* compilation for this base; our network interface includes hardware for remote read/write requests, plus counter-based synchronization support.

Finally, to evaluate the effectiveness of this approach, we simulate and measure our compiled C\* benchmarks on a traditional message-passing interface as well as our language-oriented design. These measurements demonstrate that our design is effective at reducing communication-related CPU overhead; for example, traffic between the CPU and network interface is reduced by 50 to 90 percent on these benchmarks.

#### 1.2 Related Work

Much research has been done in the past to improve performance of both shared-memory and message-passing architectures. For message-passing systems, researchers have largely focused on reducing the high per-message overhead typically found in message-passing systems. For example, active messages [von Eicken et al. 92] are a low-level transport mechanism that achieves low latency by efficiently dispatching to a message handler on the receiving node. Felten [Felten 93a] proposes using a *protocol compiler* to custom-generate message-passing protocols for a given program and thus reduce protocol overhead.

The above two approaches rely entirely on software techniques; however, hardware approaches have been suggested as well. For example, the Shrimp architecture [Blumrich et al. 94] implements a low-overhead data transport mechanism which for selected

memory pages automatically forwards a processor's store operations to other nodes. The resulting system shares some of the characteristics of remote-memory and shared-memory architectures.

There also is a large body of work aimed at improving the performance of cachecoherent shared-memory architectures. For example, researchers have studied adaptive or user/compiler selectable cache coherence mechanisms that use different coherency protocols for different sharing patterns [Carter et al. 91, Bennett et al. 92, Stenstrom et al. 93]. Some machines like the KSR-1 [KSR 92] provide processor instructions to prefetch or poststore data, or load data in a state that facilitates future writes. Most of these techniques try to improve performance by giving the application more explicit control over how and when data is moved between processing nodes. As a result, shared-memory systems take on some of the characteristics of message-passing systems (where data movement is entirely under explicit application control).

A related approach [Frank & Vernon 93] integrates message passing and shared memory by introducing a new cache line state, *possibly-stale*, into a conventional cache coherence protocol. The proposed architecture lets user programs move data between nodes without the overhead of cache coherence operations. At the same time, caches are kept coherent to provide a traditional shared memory model.

Relaxed memory consistency models [Gharachorloo et al. 90, Adve & Hill 90, Hutto & Ahamad 90] attempt to improve shared memory performance by allowing temporary inconsistencies among multiple copies of the same data. This is similar in nature to what happens in message-passing systems where copies of remote data are created under the control of the application program.

Yet another approach, taken by the Alewife machine, is to offer both a shared-memory system and message-passing primitives. In [Kranz et al. 93], the authors identify several scenarios where a compiler or programmer could implement operations more cheaply through message passing than through shared memory.

Finally, the FLASH [Kuskin et al. 94] and Typhoon [Reinhardt et al. 94] shared-memory architectures include fully programmable network interfaces. In principle, this would allow coherence protocols to be tailored to specific applications; it is even conceivable to turn these machines into NUMA or message-passing machines simply by reprogramming the network interfaces.

The current trends in research discussed above indicate that the different communi-

cation architectures are starting to converge. Shared-memory architectures are acquiring message-passing like features such as better user-level control over data movement, whereas message-passing architectures are striving for data transport mechanisms with low over-heads comparable to shared-memory and remote-memory architectures.

In our work, we compare these different architectures at a high level of abstraction; our goal is to clarify the tradeoffs between the architectures and point out desirable features of each architecture. Our results should be helpful in future research on communication architectures that unify the advantages of message-passing and shared-memory.

### 1.3 Contributions of this Dissertation

In this dissertation, we make the following contributions:

- We recognize that most existing communication architectures have been designed to be used directly by the programmer. However, in the future, more programs will be written in high-level parallel languages and compiled to a specific communication architecture. The compiler hides the details of the communication architecture from the programmer. We show that this change in programming style both requires and enables changes to the communication architecture in order to improve performance.

- We evaluate the strengths and weaknesses of three competing communication architectures — message-passing, remote-memory access, and cache-coherent sharedmemory — for a workload of compiled C\* programs. We show that compared to the other architectures, the message-passing model has various advantages. For example, the compiler has better control over data movement and granularity, and the run-time system can combine data transfer and synchronization in a single operation. As a result, the message-passing model requires less interconnect bandwidth and incurs lower communication latencies than the other models. In the process, we also present a strategy for obtaining meaningful comparisons across such widely differing of architectures.

- Noting that the message-passing model incurs significant per-message CPU overhead, we propose a *language-oriented* approach to designing a communication architecture. We first identify a small set of communication primitives that match the needs of the

C\* compiler. We then present the design of a network interface for a distributedmemory architecture that is tuned to those communication primitives. Together with a compilation approach normally used on shared-memory machines, we are able to retain the above advantages of the message-passing model while drastically reducing the per-message CPU overhead.

#### 1.4 Organization

The remainder of this dissertation is organized as follows. In Chapter 2, we discuss parallel machine architecture, which sets up the hardware framework for our studies. In Chapter 3, we describe the C\* language and highlight its close similarity to High Performance Fortran, another data-parallel language. We then outline, in Chapter 4, how our compiler translates C\* for different target communication architectures. In Chapter 5, we evaluate the relative strengths and weaknesses of three different communication architectures message-passing, remote-memory access, and cache-coherent shared memory. Our results show that the message-passing model generates less interconnect traffic, sends fewer messages and incurs less network latency than either of the competing models, primarily because it offers the compiler better control over data movement and granularity of communication. These findings imply that message-passing has some inherent advantages over the other models, at least for the benchmarks studied. In practice, however, this advantage can not currently be realized, due to the extremely high per-message CPU overhad in existing message-passing systems. In Chapter 6, we propose a language-oriented approach to designing a communication architecture. Our network interface includes hardware support for a small set of communication primitives that match the needs of the C\* compiler. Our simulations show that our design retains the advantages of the message-passing model while drastically reducing the per-message CPU overhad. We summarize our results, present our conclusions and discuss future work in Chapter 7.

# Chapter 2

# **ARCHITECTURAL FRAMEWORK**

Figure 2.1 shows an MIMD parallel computer, organized into three major component groups: *interconnection network, processing nodes* and *network interfaces* ("NI"). The network interfaces connect the processing nodes to the interconnect. In this chapter, we describe some of the architectural tradeoffs for each of the three components. Many of the design decisions are beyond the scope of this dissertation so we discuss them only briefly in order to provide a framework for our architectural research; we focus primarily on the network interface.

#### 2.1 Processing Nodes

A fundamental decision in designing the processing node is whether to use commodity or custom processors. A custom processor design can improve communication performance; for example, the architect can integrate the network interface more tightly with the CPU [Henry & Joerg 92a], or include special-purpose communication instructions in the CPU. The Kendall Square KSR-1 shared-memory computer [KSR 92] uses both approaches; its processors provide instructions for prefetching or post-storing cache lines, plus a host of instructions that control the memory system, especially the caching strategy. Different variants of the load instruction exist that can request a *writable* copy of a cache line (useful if the cache line is written later), or specify that the level-0 processor caches are to be bypassed by the access. The designers have added these instructions to the processor in order to provide the programmer or compiler with better control over data movement, with the ultimate goal of improving performance.

However, many of these functions can also be implemented on systems that use only commodity processors — albeit possibly with slightly lower performance. For example, the operating system can create multiple virtual memory mappings for a given area of physical memory, with each mapping providing different access semantics. Performance may not match that of special-purpose load and store instructions, since the processor must likely perform more address arithmetic to access the different mappings. Likewise, the network

Figure 2.1: A generic parallel machine.

interface can be made accessible as a memory-mapped device, such that the processor can initiate special operations (e.g., prefetching or flushing data) by writing memory-mapped control registers in the network interface. Again, the performance of off-chip logic may be worse than dedicated on-chip hardware, but both designs provide the same functionality.

Using off-the-shelf processors reduces overall design time for the machine and results in faster time-to-market. In fact, most existing parallel computers, such as Intel's series of message-passing machines [Arlauskas 88, Bokhari 90, Intel 91b, Intel 91a], the Thinking Machines CM-5 [TMC 91b], or the Cray T3D [Cray 93] (a NUMA machine), use processing nodes built around a commercial off-the-shelf microprocessor. Instead of requiring special-purpose processor instructions, these machines control communication through hardware external to the processor.

We conclude that the choice between custom or commodity processors is not likely to affect *functionality*, though it could possibly affect the speed at which some communication operations can be executed. In our studies, we focus on the functionality of the communication architecture, and abstract implementation-dependent details such as timing; our results apply equally well to either design alternative.

#### 2.2 Interconnection Network

The *interconnection network* is the physical substrate for moving data between processing nodes. Some key design decisions for the network are its *topology*, *reliability*, *routing strategy* and *packet size* (where applicable). In this section, we discuss some of the tradeoffs and how they interact with the design of network interfaces, described in the next section.

#### *Reliability*

Different networks offer different degrees of *reliability*. For example, due to congestion or transmission errors, the network may lose or corrupt data packets, or it may deliver spurious messages; the network may or may not detect and report these conditions. ATM network switches [Minzer 89] are allowed to "drop" packets without notification if network congestion gets too high.

If the network does not deal with such events, the communication endpoints (i.e., the NI or processing node) must execute a protocol that can handle them. Note that this involves work beyond the actual data transfer — extra processing time in the NI or node, plus possibly transmission of additional protocol messages. If the network can lose packets, the sender must be prepared to re-send a given message until it has received an *acknowledgement* that the message has indeed been delivered. Usually, the sender must save a *copy* of each message until it is acknowledged; this in turn may incur overhead for managing the required buffer space. Brustoloni and Bershad [Brustoloni & Bershad 92] have developed an efficient protocol for ATM-based networks that can handle message loss.

For our studies, we assume that the communication primitives used by the programmer or compiler are reliable, i.e., the network neither loses nor corrupts messages, and it does not introduce spurious messages.

#### Topology

Many different network topologies have been explored in the literature. Some topologies, for example buses and rings, provide inherent broadcast capabilities, whereas others, such as meshes, hypercubes or trees are point-to-point interconnects. Different topologies have different scaling characteristics, and often perform particularly well on some set of communication patterns — e.g., 2-D nearest-neighbor communication maps well onto mesh

interconnects. The topology of the network does not significantly affect the design of the network interface (though the NI designer may wish to include some mechanism to access the interconnect's broadcast capabilities, if applicable.) For this reason, we do not assume any particular network topology in our studies; the results we present will be independent of topology though they may translate into different execution times depending on the topology. We do, however, examine the impact of broadcast capability.

#### Routing and Ordering

Networks use a *routing* algorithm to direct messages from their source node to their destination. We consider two important classes of routing strategies: *oblivious* and *adaptive* algorithms. Given a source and destination node number for a data packet, an oblivious algorithm will always choose the same path for the packet, whereas an adaptive algorithm may route the packet along any of several paths, depending on network load. Adaptive routing algorithms have the advantage that they may use the interconnect's aggregate bandwidth more efficiently [Ngai & Seitz 89, Snyder 92, Konstantinidou & Snyder 91]. However, they also do not generally guarantee *FIFO* delivery of messages; in other words, if node A sends messages  $m_1$  and  $m_2$  to node B in that order, the messages may arrive in reverse order at node B.

Clearly, this can be a problem for application programs. For example, it is harder to implement efficiently a sequentially consistent shared-memory system if data packets can be delivered out of order [Thapar et al. 93]. Weaker memory consistency models [Hutto & Ahamad 90, Gharachorloo et al. 90] may be able to tolerate out-of-order delivery more easily.

Note that one can implement in-order message delivery on top of a network that delivers messages out of order, for example by adding sequence numbers to packet headers, and by reordering packets according to the sequence numbers at the receiving node. However, this approach requires the receiver to buffer packets that arrive "early" and hence also incurs overhead (processing time and possibly extra protocol messages) for managing the buffer space.

Except where noted otherwise, we assume that the communication primitives used by the programmer or compiler guarantee in-order message delivery.

#### Packet Size

Modern networks using packet-switching techniques have to split large messages into smaller *packets* that are then routed through the network. The CPU or NI of the sender of a large message must perform *packetization* (i.e., split the message body into multiple small packets), and the receiver must generally reassemble (*unpacketize*) the message from the individual packets.<sup>1</sup> Note that even with FIFO delivery in the network, a node may receive packets from different messages (sent by different nodes) *interleaved* with each other. Some programming models (including "traditional" message-passing) require receipt of a message to be *atomic*. Providing those semantics in the presence of packetization again incurs buffering and protocol overhead. Clearly, the larger the packet size, the less packetization-related overhead is incurred. Also, larger packet sizes amortize any message header overhead over a larger body. On the other hand, smaller packets may be easier to route.

A network's packet size may further be *fixed* or *variable* — in the former case, all packets sent through the network are of one fixed size, even if only part of the packet body carries useful data. In the latter approach, the packet header includes a field indicating the size of the packet body; this may result in more efficient utilization of the network's bandwidth. Overall, there appears to be no clear consensus which of these approaches is better, or what packet sizes are desirable; in fact, the "ideal" packet size depends heavily on the workload [Cypher et al. 93]. In our work, we therefore examine different packet sizes.

#### Special-Purpose Networks

Some machines, such as the Thinking Machines CM-5 [TMC 91b] or the Cray T3D [Cray 93], use dedicated networks for certain communication operations. For example, the CM-5 includes a *control network* that has been specifically optimized to perform efficient reduction and broadcast operations. Similarly, the T3D has a *synchronization* network that provides very low-latency barrier synchronization operations. In both cases, these special-purpose networks have been included in order to improve the performance of some common communication operations.

<sup>&</sup>lt;sup>1</sup> Note the interaction between packetization and out-of-order delivery: due to the former, a large message must be split into separate packets, and due to the latter, the packets may arrive at the receiver in arbitrary order, thus complicating unpacketization.

However, this can be a rather expensive approach, and a dedicated synchronization network may not always result in as significant a performance improvement as expected. For example, on the Cray T3D, the barrier hardware propagates the signal throughout a 256-node machine in 26 cycles, yet the barrier routine takes about 240 cycles because it has to flush the write buffer and wait for asynchronous remote writes to complete. The write messages, of course, propagate through the *data* network which has much higher latency than the dedicated barrier network [Barrusio 94]. This drastically limits the potential performance gains from the dedicated network.

#### Protection

Parallel machines that support time- or space-sharing among multiple users must address the issue of protecting different jobs from each other. One user's job should not be allowed to send messages to another user's job. Likewise, the network traffic generated by one job should not keep another job from making progress, e.g., by deadlocking the network. Solving this problem may in general require cooperation between the network interface and the network.

The topology of the CM-5's network makes it possible to partition the machine such that two different partitions do not physically share any part of the network. By preventing users from sending messages to nodes in a different partition (this is implemented in the NI) and by gang-scheduling jobs within each partition (implemented by the operating system), different jobs cannot interfere with each other. To simplify gang-scheduling, the CM-5 network provides a mechanism that allows the operating system to drain the network of all messages from one job before context-switching to another job.

On shared-memory machines, the operating system can use the protection mechanism of the virtual memory system to keep different jobs from accessing each other's memory. However, as long as nodes are allowed to generate an arbitrary number of communication requests, it is still possible for one job to slow down another job's progress by causing congestion in shared portions of the interconnect.

Protection is largely independent of the tradeoffs we study in this dissertation, so we do not further explore the issue.

#### 2.3 Network Interface

The *network interface* ("NI" for short) provides the *interface* that the processing nodes use to *inject* and *extract* messages into and out of the network. More than any other component, the network interface defines the *communication architecture* of a parallel machine. Depending on the NI, the machine depicted in Figure 2.1 may be a message-passing machine, a remote memory access machine (also sometimes called NUMA for Non Uniform Memory Access), or a cache-coherent shared-memory machine. The complexity of the NI varies dramatically depending on what communication architecture it implements.

#### Message-Passing

For a message-passing communication architecture, the NI can be very simple. For example, the NI on the message-passing Intel iPSC/860 consists of little more than two FIFO buffers and some control circuitry. The *receive* FIFO accumulates incoming data from the network and the *send* FIFO holds data that is to be injected into the network. The processing node accesses the network interface through a set of memory-mapped NI registers. Reading and writing these registers allows the CPU to inject data into the *send* FIFO and extract data from the *receive* FIFO. Other NI registers hold information about the status of the FIFOs or allow the processor to control the NI's mode of operation; e.g., whether or not to interrupt the CPU when the *receive* FIFO fills up. A traditional message-passing library (like Intel's NX [Pierce 88] or Thinking Machines' CMMD [TMC 92]) can be implemented on top of these primitives to provide higher levels of abstraction to the programmer. Some machines include DMA hardware to speed transfer of data between main memory and NI. Generally, DMA operations have to be initiated by the CPU for each packet sent or received, therefore such DMA support is less useful for small packets.

#### Remote Memory

In a remote memory architecture, processors communicate by accessing a (physically distributed) shared memory space through load and store instructions. A reference to data that resides on a remote node automatically generates a message to read or write the desired remote data; references to local data are directly satisfied by the node's own memory. To implement such a communication architecture, the NI becomes somewhat more complex. For example, the NI needs to observe the processor's memory references

(e.g., by snooping on the processing node's memory bus), and it must be able to determine, based on the observed address, whether data resides on the local node or a remote node. A simple solution distributes memory among nodes such that the high order bits of a physical address indicate the processing node that holds that memory location.<sup>2</sup> For remote accesses, the NI then needs to create a message, inject it into the network, and possibly stall the processor until the operation is complete. The NI must also be able to access the processing node's main memory in order to reply to memory requests from other nodes.

#### Cache-Coherent Shared Memory

Cache-coherent shared-memory machines use essentially the same communication interface as remote-memory machines. However, the NI now includes *caches* (or uses the node's main memory as a cache) that can hold data from remote nodes, and the NI must implement some *cache coherence protocol* to keep all caches in the system consistent with each other.<sup>3</sup>

In our work, we examine two classes of cache coherence protocols: *write-invalidate* and *write-update*. In a write-invalidate protocol, a processing node that is about to write to a cache line needs to first *invalidate* all other copies of that cache line, to ensure it has an exclusive (and hence writable) copy. This involves sending invalidation messages to all other nodes that hold a copy of the cache line, and possibly waiting for acknowledgement messages to indicate that the invalidation has been performed. In a write-update protocol, more than one node may keep a writable copy of a cache line. Whenever the cache line is written, the changes are forwarded to all other nodes holding a copy of the line.

The choice of interconnect may influence the design of the cache coherency protocol. For example, if the network supports efficient broadcast operations, then a *snoopy* cache coherence protocol (e.g. [McCreight 84]) can be used. Otherwise, *directory-based* protocols (such as [Censier & Feautrier 78]) are more attractive. . However, the difference

<sup>&</sup>lt;sup>2</sup> The Cray T3D uses an approach similar in spirit. However, the T3D is supposed to scale to large numbers of nodes, and sacrificing enough high-order physical address bits to encode that many processing node numbers would reduce the available per-node physical address space by too much. Instead, the T3D dedicates a smaller number of high-order address bits to encode a node identifier, and each processing node uses a lookup table (the "TLB Annex") [MacDonald & Barrusio 94] to translate this identifier into a full node number.

<sup>&</sup>lt;sup>3</sup> Such as design usually requires a very tight coupling between the NI and the processing node's memory system, so one could argue whether the caches are part of the NI or part of the processing node. For the purpose of this discussion, we consider the caches for remote data a part of the NI.

between snoopy and directory-based protocols does not affect the programmer's view of the communication interface, so we do not explore this otherwise very important issue further.

In most existing shared-memory machines, all data in the system's caches is backed by main memory. In the case where main memory is physically distributed with the processing nodes, e.g. on the Stanford DASH [Lenoski et al. 92], each cache line has a *home* node, namely the processing node holding the portion of main memory that backs the cache line. To access data in a given cache line, processing nodes send their requests to the home node, which keeps track of all copies of the line and can properly serialize accesses to the cache line.

A different approach is taken in so-called COMA (Cache-Only Memory Architecture) shared-memory machines, such as the DDM [Hagersten 92a] or the KSR-1 [KSR 92]. These systems do not include any "main memory"; data exists *only* in the caches, and cache lines do not have a home node — in other words, there is no *fixed* node in the system that at all times keeps track of a given cache line's state or location, or that serializes accesses to the line. Generally, accessing data therefore involves some form of *search* for a copy of the cache line. In the case of the KSR-1, the search mechanism takes advantage of the inherent broadcast capabilities of the underlying interconnect, which has a ring topology.<sup>4</sup>

In our experiments, we will study both COMA and more conventional cache-coherent shared-memory machines, and we will examine both write-invalidate and write-update protocols.

#### 2.4 Summary

The hardware components of a parallel computer can be organized into three groups: an interconnection network, and a set of processing nodes and network interfaces. We have described some of the design tradeoffs for each of these components.

Our goal is to study the interaction of communication architecture (i.e., the communication interface available to the programmer or compiler) and programming languages. We focus on the design of the network interface, which more than any other component defines a machine's communication architecture.

Issues of programming node and network design are largely orthogonal to our studies.

<sup>&</sup>lt;sup>4</sup> The KSR-1 can actually use two levels of rings, and it maintains directories at the up/down-links between the levels, to determine whether a request needs to be propagated to the other rings as well.

All NI designs we will discuss in this dissertation are intended to work well with offthe-shelf processors. Unless otherwise stated, we assume in our experiments that the underlying interconnection network is *reliable* (e.g., it does not lose, duplicate, or corrupt packets without signalling an error) and provides *FIFO ordering*.

# Chapter 3

# **DATA-PARALLEL LANGUAGES**

We have chosen C\* [Rose & Steele Jr. 87, TMC 90], a *data-parallel* language, as the high-level parallel language for our experiments. There exists a significant body of work on C\* as well as other data-parallel languages such as Force [Jordan 87], Dino [Rosing et al. 90], Kali [Koelbel & Mehrotra 91], Vienna Fortran [Chapman et al. 92] or High-Performance Fortran (HPF) [HPFF 93], to name just a few. This reflects the growing popularity of this type of language. The following two properties are shared by almost all (imperative) data-parallel languages.

- Parallelism is obtained by performing similar (or identical) operations in parallel on the elements of a large data set. The elementwise addition of vectors would be a trivial example.

- The language semantics offer the *illusion* of *lockstep execution*; in other words, no matter how many processors are used, conceptually there is a single "program counter." This execution model avoids race conditions and thus greatly simplifies the understanding and debugging of data-parallel programs.

While the data-parallel model of execution is not as general as arbitrary MIMD computation, it is nonetheless a very powerful model. A study by Fox [Fox 88] showed that 70 out of 84 scientific applications studied, or over 80%, fit the data-parallel model. Klaiber and Frankel [Klaiber & Frankel 93] have demonstrated that even an application that intuitively does not seem to fit the data-parallel model — a distributed event-driven simulation — can be expressed cleanly and efficiently in a data-parallel language.

Several data-parallel languages, including an older version of C\* [Rose & Steele Jr. 87], originated as a programming language for SIMD machines. However, researchers have shown [Hatcher & Quinn 91, Rosing et al. 90, Koelbel & Mehrotra 91, Chapman et al. 92] that data-parallel programs can be compiled to run efficiently on MIMD hardware as well — both distributed-memory and shared-memory architectures. To do this, the compiler generates code that includes communication and synchronization operations

carefully chosen to preserve the lockstep semantics of the data-parallel language while also minimizing the total amount of communication.

Compilers for data-parallel languages essentially produce SPMD (single-program, multiple-data) style code, a common programming paradigm on MIMD machines. Parallelizing compilers for sequential languages, such as Paradigm [Su et al. 93], generate similar code. In fact, since most parallelizing compilers exploit mainly data parallelism (e.g., by parallelizing loops), we expect programs generated this way to exhibit execution behavior similar to compiled programs written in high-level data-parallel languages.

In Section 3.1, we give an overview of the C\* language, and we draw a brief comparison between C\* and High Performance Fortran (HPF) in Section 3.2, demonstrating the similarity of the two languages.

### **3.1** The C\* Language

Several languages featuring data-parallel execution have been proposed over the last years. For this work, we chose the "new" revision of C\* [TMC 90, TMC 91a] as a representative data-parallel language. As we will see shortly, C\*'s communication operations are typical of what we would expect from other data-parallel languages, hence our findings should extend to those languages as well. We particularly highlight the similarity between C\* and HPF in the next section.

Significant work has been done on the compilation of an older version of C\* (defined in [Rose & Steele Jr. 87]) for both distributed-memory and shared-memory multiprocessors; see for example [Hatcher & Quinn 91] for a summary. For a detailed description of the current language, the reader is referred to [TMC 91a]; we give a brief overview here.

C\* distinguishes between *scalar* and *parallel* variables; the latter have a *shape* associated with them that describes how the data is organized. Attributes of a shape are its rank, layout and number of *positions*; there is one *virtual processor* (VP) per position. Shapes serve as templates to declare parallel variables of that shape: when a parallel variable of some shape *S* is declared, one element of the variable is allocated in each position (i.e., each VP) of the shape. Parallel variables of identical shape are laid out identically, meaning corresponding positions of all parallel variables of a given shape are mapped to the same VP.

The compiler and run-time system create the final data distribution by mapping the virtual processors onto the physical processors. C\* does not provide mechanisms for explicitly specifying this mapping, though the programmer can provide hints. Unfortunately,

there is no way to specify the alignment of two different shapes with respect to each other.

To operate on parallel data, the programmer selects a *current shape* using the with statement. Simple operations such as addition, when applied to parallel data, are executed in parallel for each position in the current shape.

The following example first declares the shape MatrixShape as a two-dimensional  $(100 \times 100)$  grid, and then declares two parallel variables, a and b, of type double and shape MatrixShape. Since a and b have the same shape, corresponding positions of the two variables are co-located in the same virtual processor. I.e., the virtual processor at position (i, j) in the shape will hold the matrix elements  $a_{i,j}$  and  $b_{i,j}$ . When data is co-located on the same virtual processor, it is also co-located on the same physical processor, hence the elementwise addition performed in the example below does not generate any inter-processor communication.

```

shape [100][100]MatrixShape;

double:MatrixShape a, b;

with (MatrixShape)

a = a + b;

```

Control flow in C\* is sequential, i.e., from the programmer's point of view, conditional branches, procedure calls, etc. are followed by all processors. In fact, virtual processors behave as if they were executing code synchronously. Parallel operations can be *contextualized* inside a where statement by specifying a parallel boolean expression that determines which virtual processors are "active". Conceptually, a where statement first executes the where branch, then the else branch, with parallel operations restricted to the virtual processors on which the condition evaluates to true and false respectively.<sup>1</sup> The following example computes the square root of the absolute value of each element in the matrix a.

```

with (MatrixShape)

where (a >= 0.0) b = sqrt(a);

else b = sqrt(-a);

```

Communication in C\* is performed by *send* or *get* operations, which are written as parallel *left index* expressions, using a syntax reminiscent of array references. The code below

<sup>&</sup>lt;sup>1</sup> The semantics of C\* specify that scalar code inside branches of a where statement is *always* executed, i.e., independent of the condition in the where. This is in keeping with C\*'s "global model of execution" [TMC 91a].

transposes matrix a by sending each element at position (i, j) to position (j, i). Matrix b is transposed using an equivalent (but not necessarily equally efficient) get operation. The parallel expression pcoord(i) evaluates to a position's index along dimension i of the current shape, i.e., for C\*'s row-major layout, pcoord(0) yields an element's row number in the matrix and pcoord(1) yields the column number. Send and get operations are atomic in that they behave as though all data elements were sent simultaneously.

```

with (MatrixShape) {

[pcoord(1)][pcoord(0)]a = a;

b = [pcoord(1)][pcoord(0)]b;

}

```

In the case where multiple VPs send data to the same destination VP, C\*'s *combining send* operations allow the programmer to specify a binary combining operation, such as addition, which will be performed on all data arriving at the same destination VP. By default, the receiving VP may arbitrarily choose one of the conflicting data items.

In addition, C\* provides powerful *reduction* operations by overloading the C language's "embedded assignment" operators.<sup>2</sup> A simple example that computes the sum of all elements in matrix a is given below.

```

double elementSum;

with (MatrixShape)

elementSum = (+= a);

```

Finally, C\* provides access to individual elements of parallel data, which may require data to be broadcast to all nodes. The syntax is the same as a *get* or *send* operation, but all left indices are *scalar* rather than parallel expressions (note that it is trivial for a compiler to detect this). The code fragment below divides all matrix elements by the element in the upper left corner of the matrix. Since the matrix is distributed across nodes but all nodes need the value of  $a_{0,0}$ , that matrix element needs to be broadcast.

```

with (MatrixShape) {

a /= [0][0]a;

}

```

<sup>&</sup>lt;sup>2</sup> More complex reduction and scan operations are available using function call syntax, i.e., the language provides no special operators for them.

Functions in C\* can take parallel arguments and return parallel results. For example, the parallel version of the sin function is declared as

```

double:current sin(double:current);

```

where current is a reserved word referring to the shape that is in effect at the time of the function call. The syntax for calling parallel functions is the same as that for scalar functions; e.g. to compute the sine of all non-negative elements in matrix a, one would write

```

with (MatrixShape)

where (a >= 0.0) a = sin(a);

```

Given the synchronous model of execution, C\* programs do not exhibit race conditions, and execution does not depend on nondeterministic events such as message arrival orders.<sup>3</sup> The simple programming model of sequential control flow coupled with deterministic execution makes programming and debugging of C\* programs almost as easy as for purely sequential languages. While requiring that all communication be explicit in the source code does place additional burden on the programmer, it also provides the programmer with a clear performance model, exactly *because* any potentially expensive communication operations are clearly visible in the code. One drawback of C\* (or similar languages) is that sometimes the synchronous semantics overly constrain a solution, as one cannot efficiently express arbitrary asynchronous operations. Naïve compilation may exacerbate this problem, but some language extensions and compiler techniques can alleviate the problem [Klaiber & Frankel 93].

#### 3.2 C\* versus HPF

The C\* language originated as a language for SIMD architectures, so there may be concerns over how well it represents other data-parallel languages. In this section, we compare C\* with the more recently developed High Performance Fortran (HPF), another data-parallel language. We show that, despite their different syntax, heritage and emphasis, both C\* and HPF share important characteristics, especially regarding communication. We provide

<sup>&</sup>lt;sup>3</sup> The one obvious exception is the *combining* send operation. However, it is easy to make this a deterministic operation as well — in fact, Thinking Machines' C\* implementation does just that.

this comparison as a "proof-by-example" that our findings obtained from analyzing C\* benchmarks and compilation should extend to other data-parallel languages.

As we have seen, variables in C\* are explicitly declared parallel by associating a *shape* with them. We can think of the shape as a set of virtual processors, with each virtual processor holding one element of the parallel variable. The parallelism in operations on parallel variables is implicit in C\* — the programmer specifies no looping construct or index variables. For example, the code below declares two matrices a and b, and performs elementwise addition in parallel.

```

shape [100][100]MatrixShape;

float:MatrixShape a, b;

with (MatrixShape) {

a = a + b;

}

```

In contrast, parallel variables in HPF are first declared as arrays, and then distributed across processors. In HPF, data distribution is a two-step process: the programmer can specify how to distribute the array over a set of *abstract processors*, which the compiler (possibly in cooperation with the run-time system) then maps onto physical processors. HPF's abstract processors are similar to virtual processors in C\*. The key difference is that in C\*, the mapping of data to VPs is fixed — exactly one element per VP. To operate on parallel variables, HPF provides a parallel looping statement, FORALL. Assuming there are 10 abstract processors, the above C\* example could be written in HPF as follows:

```

REAL a(100,100), b(100,100)

!HPF$ PROCESSORS procs(10)

!HPF$ DISTRIBUTE (BLOCK,*) ONTO procs :: a, b

FORALL (i=1:100, j=1:100) a(i,j) = a(i,j) + b(i,j)

```

Certain forms of parallel operations can be expressed more conveniently using the Fortran 90 triplet notation. For example, we could replace the FORALL loop in the above code by the statement

HPF's approach to data distribution is more complex and flexible than the one taken by C\*, but the end result is the same: elements of a parallel variable are distributed among a

set of physical processors. The biggest drawback of C\* is probably that one cannot align different shapes with respect to each other. The C\* benchmarks we study do not require particularly elaborate data distributions, and would not benefit from HPF's added flexibility. Also, researchers have recently had great success in deriving data distributions *automatically* [Su et al. 93]; this may obviate HPF's complex data distribution specifications.

To express communication,  $C^*$  and HPF again use different syntax but very similar semantics.  $C^*$  uses *left index* expressions to describe communication operations, whereas in HPF, any array index operation potentially causes communication. For example, the  $C^*$  code to set b to the transpose of matrix a (using a send operation)

```

with (MatrixShape) {

[pcoord(1)][pcoord(0)]b = a;

}

```

has the following equivalent in HPF:

```

FORALL (i=1:100, j=1:100)

b(j,i) = a(i,j)

END FORALL

```

Like C\*, HPF provides reduction operations, and accessing individual elements of a parallel variable (either through the Fortran 90 SPREAD operation or through array indexing) may require broadcast operations. While HPF does not include an operation corresponding to the C\* *combining* send, other communication operations are semantically comparable, and we argue that the two languages' demands on the communication substrate should likewise be similar.

Since C\* parallel operations and HPF FORALL loops are semantically equivalent, and since communication operations are also comparable in both languages, the overall compilation strategy and communication requirements for C\* and HPF are essentially the same.

We conclude that despite different heritage and emphasis, there are many similarities between HPF and C\*, including the computation and communication model. Therefore, we postulate that the findings we present in chapters 5 and 6 will apply to data-parallel languages other than C\* as well (at the very least to HPF).

## 3.3 Summary

The C\* language originated as a language for SIMD architectures, whereas more recent data-parallel languages, such as High Performance Fortran (HPF), have been designed from the start with MIMD target machines in mind. We have compared C\* with HPF. Though the latter places a much heavier emphasis on allowing the programmer to specify details of how to distribute parallel data, we have found that the two languages are in fact very similar. Specifically, we argue that the demands on the communication architecture are comparable, hence the results (obtained from C\* benchmarks) we present in the core of this dissertation should also apply to HPF, and likely to other data-parallel languages as well.

# Chapter 4

# **THE C\* COMPILER**

In this chapter, we outline our compilation strategy for C\*. Our C\* compiler is based on a recent version of the compiler by Hatcher and Quinn [Quinn et al. 88, Hatcher et al. 91, Hatcher & Quinn 91] that we have modified for our purposes. The overall approach is to translate C\* into mostly machine-independent C code that makes calls to run-time libraries for all communication and synchronization operations. The resulting code is then linked with architecture-specific run-time libraries.<sup>1</sup> Figure 4.1 outlines the compilation process. The simulation framework, used to gather our measurements, is described in section 5.3.

Our C\* compiler generates code for an abstract *communication model* which the runtime libraries map onto the target machine's communication architecture. The compiler's communication model need not be identical to the target communication architecture (in fact, it may help to hide some details of the hardware), but of course there must exist an efficient mapping from the former onto the latter. In Section 4.1, we contrast existing communication models for shared-memory and distributed memory targets; our compiler uses a hybrid of these models. In Section 4.2, we then describe in more detail the different tasks that our compiler performs, and we give a very high-level outline of the run-time libraries.

The experiments described later in this dissertation focus on communication operations rather than efficient code generation for *local* (i.e., non-communication) operations. In fact, we explicitly ignore time spent performing computation, so we need not concern ourselves with "traditional" optimizations or C\*-specific optimizations (such as reducing the cost of emulating virtual processors) that improve execution speed of local operations.

<sup>&</sup>lt;sup>1</sup> In practice, one would presumably inline most of the communication operations in order to obtain better performance, but this was not necessary for the purpose of this dissertation.

Figure 4.1: Compiling C\* for multiple target architectures.

## 4.1 Alternative Communication Models

Hatcher and Quinn describe two alternative approaches for compiling  $C^*$  for sharedmemory and distributed-memory targets, respectively [Hatcher & Quinn 91]. In this section, we briefly review and contrast their approaches, and then outline the compilation strategy of the  $C^*$  compiler used in this dissertation.

### 4.1.1 Compiling for a Shared-Memory Target

In a shared-memory architecture, all nodes can access each other's memory through load and store instructions. When generating code for such an architecture, the compiler need not treat accesses to remote data any differently from accesses to local data. This greatly simplifies how the compiler handles C\* communication operations, since C\* get and send operations translate directly into load and store instructions. However, the compiler must insert explicit synchronization operations in the generated code to prevent *race conditions*. Hatcher and Quinn describe this approach in [Hatcher et al. 91].

Consider the C\* code in Figure 4.2a, where each VP sends a copy of its y variable to its left neighbor, which stores the data in its x variable. To simplify the following discussion,

we ignore effects at the ends of the VP array, and assume one virtual processor per physical processor, i.e., each physical processor "owns" one element of the parallel variables x and y.

Figure 4.2b represents the corresponding C code generated for a shared-memory machine. This code is executed independently on all processing nodes; self contains the processor number. The parallel variables have been transformed into arrays located in the shared address space,<sup>2</sup> and the C\* send to variable x has been translated directly into a variable access. Note that the compiler had to insert a call to Synchronize in order to ensure that processors do not read "their" element in x until it has first been written by their neighboring processor. To preserve the inter-node data dependencies in our example, Synchronize must make the calling processor wait until its right neighbor has also called Synchronize.

As this example shows, the main task when compiling for a shared-memory architecture is to determine a minimal set of points where synchronization is required.

# 4.1.2 Compiling for a Distributed-Memory Target

For distributed-memory targets, message-passing has traditionally been the communication model of choice (e.g., [Chapman et al. 92, Su et al. 93, Quinn et al. 88]). By analyzing the accesses to parallel variables, the compiler (or the run-time system) determines the set of data elements that must be communicated between nodes, and emits matching pairs of message-passing msg\_send and msg\_recv calls to perform the communication.

An advantage of this approach is that the message-passing model combines data transfer and synchronization in one operation. Hence, the processors need not perform synchronization as a separate operation, as is the case in a shared-memory communication model. Also, the generated code can take advantage of the "just-in-time" delivery semantics of messages: a node can send data to another node even before the receiver has posted a matching msg\_recv operation. The message-passing library (or operating system) on the receiver will simply buffer the incoming message until it is needed by the application program. As a result, there is more "slack" in the synchronization between the two nodes, which may help hide temporary load imbalances, and increases potential for overlap of

<sup>&</sup>lt;sup>2</sup> Note that unless the cache line size is  $\leq$  the size of an integer, a data distribution of one array element per processor is going to cause *false sharing*. We will describe shortly how our compiler addresses this problem.

```

shape [N_proc]S;

int:S x,y;

[.-1]x = y;

use(x);

(a) original C* code.

```

```

SHARED int x[N_proc], y[N_proc];

x[self-1] = y[self];

Synchronize();

use(x[self]);

```

(b) code generated for shared-memory model.

```

int x[1], y[1];

msg_send(self-1, &y[0], sizeof(int));

msg_recv(self+1, &x[0], sizeof(int));

use(x[0]);

```

(c) code generated for message-passing model.

```

int x[1], y[1];

remote_write(remote_addr(self-1, "x[0]"), y[0]);

Synchronize();

use(x[0]);

```

(d) code generated for remote-memory model.

Figure 4.2: Communication for different communication models.

communication and computation.

Returning to the C\* example in figure 4.2, the compiler determines that each physical processor sends one data item to its left neighbor, and receives one data item from the right neighbor. Again, we are assuming a mapping of one VP per physical processor, and we ignore effects at the ends of the VP array. Figure 4.2c shows the C code a compiler would generate for a message-passing communication model. Since the target is a distributed-memory machine where each node has its own separate address space, the compiler physically partitions the parallel variables: each processor holds one element of the variables x and y. The msg\_send and msg\_recv operations implement the communication by sending a copy of y to the left neighbor (self-1) and receiving a new value for x from the right neighbor. Note that the code does not require an explicit synchronization operation. Instead, a processor can safely continue execution as soon as the data from the right neighbor has arrived.

Unfortunately, the message-passing communication model also has several drawbacks. First, traditional message-passing incurs run-time *protocol* overhead, e.g., for managing the buffers required for the "just-in-time" delivery semantics. Felten has shown that protocol overhead degrades the performance of message-passing codes [Felten 93a]. Since the C\* communication operations read and write parallel variables that are already allocated by the compiler, most of the buffer management overhead is completely unnecessary.

Second, in a message-passing model of communication, data transfer and synchronization are *always* combined, even when only one of the two functions is needed. Since neither function is free, the processors have to perform unnecessary work; we discuss this point in more detail in Chapter 6.

Third, programs often exhibit communication patterns that cannot be analyzed at compile time. In that case, the compiler cannot determine the set of data elements that must be communicated, and hence it cannot generate the required  $msg\_send$  and  $msg\_recv$  operations. Note that this problem does not occur in the shared-memory model. The reason is that communication in the shared-memory model is *requester* based, meaning a given node can read and write another node's memory *without* the cooperation of the other node. The compiler therefore can simply emit code to perform the read or write operation. In the message-passing model, *both* nodes must actively participate in the communication: the sender must execute a  $msg\_send$ , and the receiver must execute a matching  $msg\_recv$ . To generate code for a given node A, the compiler must therefore have complete knowledge about *all* requests for *A* made by *any* of the other nodes. A general solution to this problem requires extra communication and computation at run-time, just to determine which nodes have to send which data items where [Clark et al. 92, von Hanxleden et al. 92]. To reduce this overhead, the run-time system can analyze a communication pattern once at run-time, and amortize the cost of the analysis over many reuses of the pattern [Wu et al. 91]. Also, researchers have optimized the analysis phase itself [Leung & Zahorjan 93].

However, we wish to reduce this overhead further, even in cases where the above techniques are not applicable.

#### 4.1.3 Our Compilation Strategy

We now describe the strategy our compiler uses to generate code for shared-memory and distributed-memory target architectures.

#### Distributed Memory

As we have seen above, compilation for a message-passing model is harder than for a shared-memory model, and programs that cannot be fully analyzed at compile-time may incur additional run-time communication overhead. To make things worse, traditional message-passing libraries already have a very high per-message overhead.

One reason for this is that messages are a very general mechanism for communication. Conceptually, a message *per se* has no semantics attached, and it is up the the receiver to place an interpretation on the message, and to determine how to process it. The semantics of message-passing also specify many functions besides the actual data transfer — e.g., automatic buffering of messages and implicit synchronization between sender and receiver.

However, most communication in the C\* language only requires one specific primitive operation to be performed, and there is only a small number of commonly used primitives. For example, almost all C\* communication operations involve reading or writing memory on a remote node.

Our C\* compiler therefore uses a *remote memory access* model of communication which better matches the language's communication operations. The remote memory model is very similar to the shared-memory model, in that the two fundamental communication primitives are reading and writing of memory on a remote node. To access data on a remote node, the compiler need only generate an operation on the requesting node. Since remotememory access communication does not perform implicit synchronization between sender and receiver, the compiler has to insert explicit synchronization operations to preserve inter-node data dependencies — just like it does for the shared-memory model.

In fact, as far as our compiler is concerned, compilation for the remote-memory and shared-memory models is exactly the same, since the machine-specific communication libraries hide the few remaining differences.

Figure 4.2d shows the code generated for the remote-memory access model; note the similarity between this version and the one for the shared-memory model. The expression remote\_addr(nodeno, "var") computes the address of variable var on node number nodeno, for use in the remote\_write operation. In order to obtain good performance, nodes must be able to compute this address quickly. Fortunately, this is not a problem for most regular data distributions; for irregular distributions, *all* compilation approaches will incur higher overhead for address and index calculation.