### © Copyright 1998

Theodore Haynes Romer

## Using Virtual Memory to Improve Cache and TLB Performance

by

Theodore Haynes Romer

A dissertation submitted in partial fulfillment of the requirements for the degree of

Doctor of Philosophy

University of Washington

1998

Approved by\_\_\_\_\_

(Chairperson of Supervisory Committee)

Program Authorized

to Offer Degree\_\_\_\_\_

Date\_\_\_\_\_

In presenting this dissertation in partial fulfillment of the requirements for the Doctoral degree at the University of Washington, I agree that the Library shall make its copies freely available for inspection. I further agree that extensive copying of this dissertation is allowable only for scholarly purposes, consistent with "fair use" as prescribed in the U.S. Copyright Law. Requests for copying or reproduction of this dissertation may be referred to University Microfilms, 1490 Eisenhower Place, P.O. Box 975, Ann Arbor, MI 48106, to whom the author has granted "the right to reproduce and sell (a) copies of the manuscript in microform and/or (b) printed copies of the manuscript made from microform."

Signature\_\_\_\_\_

Date\_\_\_\_\_

#### University of Washington

Abstract

#### Using Virtual Memory to Improve Cache and TLB Performance

by Theodore Haynes Romer

Chairperson of Supervisory Committee Professor Brian N. Bershad Computer Science and Engineering

This thesis introduces new operating system policies that use virtual memory to dynamically improve memory system performance. Overall application execution time is increasingly dependent on memory system performance, motivating the development of new techniques for reducing cache and translation lookaside buffer (TLB) miss rates.

My thesis is that the operating system can effectively manage cache and TLB resources at runtime on behalf of applications. I develop and evaluate two examples of operating system memory system optimizations. First, I show how the operating system can optimize TLB performance by dynamically constructing superpages. I introduce a policy that analyzes the cause of each TLB miss, and uses this information to selectively create large pages, reducing the TLB miss rate without the increase in memory consumption that would accompany a global increase in the page size. Second, I show how the operating system can optimize cache performance by dynamically remapping pages. The operating system controls which virtual pages potentially conflict in a physically indexed cache, because it controls the mapping from virtual to physical pages. I propose two techniques that inform the operating system when virtual pages are in fact resulting in conflict misses, allowing the operating system to remap conflicting pages. By exploiting the associativity inherent in the mapping from virtual pages to cache pages the operating system can eliminate cache conflict misses without the hardware cost of an associative cache.

I use both simulation and implementation to show that these techniques can improve application performance. I also show that the two techniques can be combined, resulting in a new policy that outperforms either of the separate techniques. Since these policies are implemented in the operating system, they benefit arbitrary applications, without modifying existing processors and without rewriting or recompiling existing software. As long as hardware memory system implementations provide adequate feedback and control mechanisms, the operating system can automatically improve performance by better managing available hardware resources to meet application resource requirements.

## **Table of Contents**

| List of F | igures                                               | iii |

|-----------|------------------------------------------------------|-----|

| List of T | ables                                                | v   |

| Chapter   | 1: Introduction                                      | 1   |

| 1.1       | Thesis statement and contributions                   | 3   |

| 1.2       | Thesis overview                                      | 5   |

| Chapter   | 2: Background and Related Work                       | 7   |

| 2.1       | Background                                           | 7   |

| 2.2       | Related work                                         | 16  |

| 2.3       | Evaluation of prior work                             | 20  |

| Chapter   | 3: Using Virtual Memory to Improve TLB Performance   | 23  |

| 3.1       | Introduction                                         | 23  |

| 3.2       | Methodology                                          | 28  |

| 3.3       | Policy design principles                             | 29  |

| 3.4       | Promotion policies                                   | 36  |

| 3.5       | Policy space and time costs                          | 39  |

| 3.6       | Simulation results                                   | 44  |

| 3.7       | Implementation issues                                | 48  |

| 3.8       | Open questions                                       | 54  |

| 3.9       | Conclusions                                          | 58  |

| Chapter   | 4: Using Virtual Memory to Improve Cache Performance | 59  |

| 4.1       | Introduction                                         | 59  |

| 4.2       | Policy design                                        | 63  |

| 4.3       | Experimental methodology                             | 69  |

| 4.4                                           | Policy evaluation                                                                                                                                                                                                                                                                                                                                                                                         | 73                                                                                       |

|-----------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|

| 4.5                                           | Implementation and performance                                                                                                                                                                                                                                                                                                                                                                            | 80                                                                                       |

| 4.6                                           | Conclusions                                                                                                                                                                                                                                                                                                                                                                                               | 84                                                                                       |

| Chapter                                       | 5: Using Virtual Memory and Low-Cost Hardware to Improve Cache Per-                                                                                                                                                                                                                                                                                                                                       | -                                                                                        |

|                                               | formance                                                                                                                                                                                                                                                                                                                                                                                                  | 85                                                                                       |

| 5.1                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                              | 85                                                                                       |

| 5.2                                           | The Cache Miss Lookaside Buffer                                                                                                                                                                                                                                                                                                                                                                           | 88                                                                                       |

| 5.3                                           | Policy design                                                                                                                                                                                                                                                                                                                                                                                             | 91                                                                                       |

| 5.4                                           | Policy evaluation                                                                                                                                                                                                                                                                                                                                                                                         | 93                                                                                       |

| 5.5                                           | Hardware alternatives                                                                                                                                                                                                                                                                                                                                                                                     | 98                                                                                       |

| 5.6                                           | The effect of CML Buffer design and policy parameters                                                                                                                                                                                                                                                                                                                                                     | 101                                                                                      |

| 5.7                                           | Open questions                                                                                                                                                                                                                                                                                                                                                                                            | 107                                                                                      |

| 5.8                                           | Conclusions                                                                                                                                                                                                                                                                                                                                                                                               | 108                                                                                      |

|                                               |                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                          |

| Chapter                                       | 6: Using Virtual Memory to Improve the Cache and TLB Performance of                                                                                                                                                                                                                                                                                                                                       | f                                                                                        |

| Chapter                                       | 6: Using Virtual Memory to Improve the Cache and TLB Performance of Windows Applications                                                                                                                                                                                                                                                                                                                  | f<br>109                                                                                 |

| Chapter<br>6.1                                |                                                                                                                                                                                                                                                                                                                                                                                                           | 109                                                                                      |

| Ĩ                                             | Windows Applications                                                                                                                                                                                                                                                                                                                                                                                      | 109                                                                                      |

| 6.1                                           | Windows Applications         Introduction                                                                                                                                                                                                                                                                                                                                                                 | <b>109</b><br>109                                                                        |

| 6.1<br>6.2                                    | Windows Applications         Introduction         Methodology                                                                                                                                                                                                                                                                                                                                             | <b>109</b><br>109<br>113                                                                 |

| 6.1<br>6.2                                    | Windows Applications         Introduction         Methodology         The effect of dynamic virtual memory optimizations for cache performance                                                                                                                                                                                                                                                            | <b>109</b><br>109<br>113                                                                 |

| 6.1<br>6.2<br>6.3                             | Windows Applications         Introduction         Methodology         The effect of dynamic virtual memory optimizations for cache performance         on Windows applications                                                                                                                                                                                                                            | <ul><li>109</li><li>109</li><li>113</li><li>116</li></ul>                                |

| 6.1<br>6.2<br>6.3                             | Windows Applications         Introduction         Methodology         Methodology         The effect of dynamic virtual memory optimizations for cache performance         on Windows applications         The effect of dynamic superpage construction on Windows application                                                                                                                            | <ul> <li>109</li> <li>109</li> <li>113</li> <li>116</li> <li>118</li> </ul>              |

| 6.1<br>6.2<br>6.3<br>6.4                      | Windows Applications         Introduction         Methodology         Methodology         The effect of dynamic virtual memory optimizations for cache performance         on Windows applications         The effect of dynamic superpage construction on Windows application         TLB performance                                                                                                    | <b>109</b><br>109                                                                        |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5               | Windows Applications         Introduction         Methodology         The effect of dynamic virtual memory optimizations for cache performance         on Windows applications         The effect of dynamic superpage construction on Windows application         TLB performance         Bounding TLB management overhead by throttling                                                                 | <ul> <li>109</li> <li>109</li> <li>113</li> <li>116</li> <li>118</li> <li>121</li> </ul> |

| 6.1<br>6.2<br>6.3<br>6.4<br>6.5<br>6.6<br>6.7 | Windows Applications         Introduction         Methodology         Methodology         The effect of dynamic virtual memory optimizations for cache performance         on Windows applications         The effect of dynamic superpage construction on Windows application         TLB performance         Bounding TLB management overhead by throttling         Combined TLB and cache optimization | <ul> <li>109</li> <li>113</li> <li>116</li> <li>118</li> <li>121</li> <li>125</li> </ul> |

# List of Figures

| 2-1 | Effect of page mappings on TLB performance.                              | 8   |

|-----|--------------------------------------------------------------------------|-----|

| 2-2 | Effect of virtual-to-physical mappings on cache performance              | 8   |

| 2-3 | A typical fully-associative software-filled TLB, with a single page size | 10  |

| 2-4 | Effect of TLB misses on performance on a DEC Alpha 3000/700              | 12  |

| 2-5 | A typical TLB, with support for multiple page sizes (superpages)         | 13  |

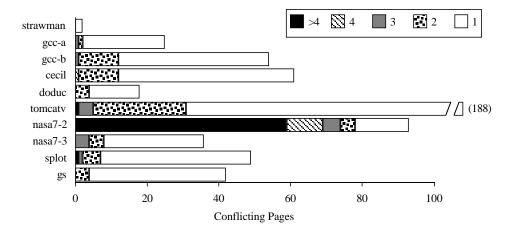

| 2-6 | Effect of conflict misses (simulated)                                    | 16  |

| 3-1 | TLB overhead as a function of memory usage overhead for a range of page  |     |

|     | sizes                                                                    | 26  |

| 3-2 | Example of prefetch and capacity charges.                                | 32  |

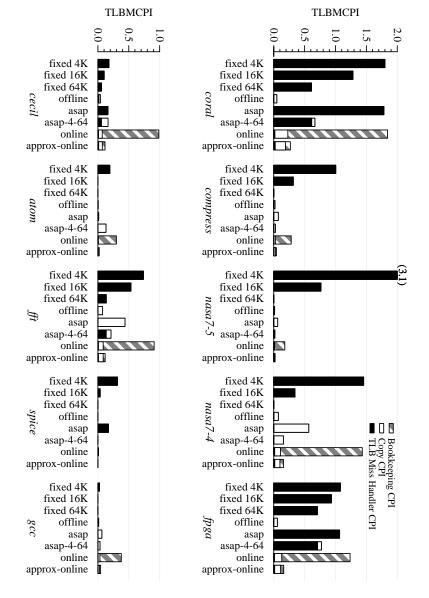

| 3-3 | Time overhead due to TLB management for each policy.                     | 45  |

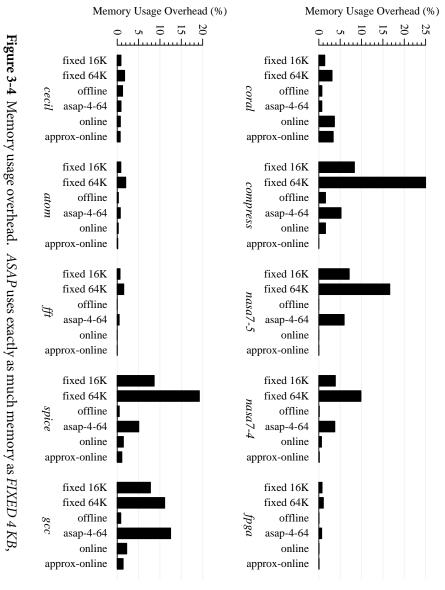

| 3-4 | Memory usage overhead                                                    | 49  |

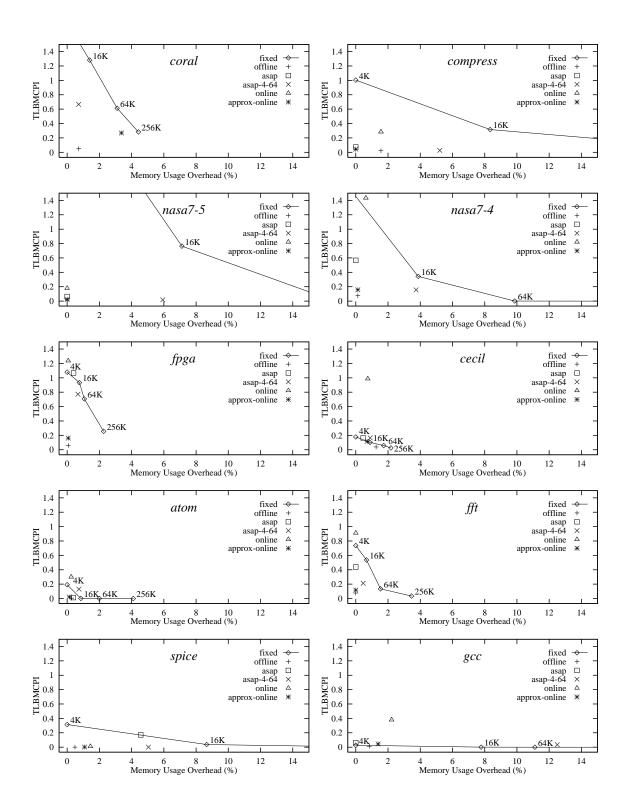

| 3-5 | Tradeoff between memory usage and TLBMCPI                                | 50  |

| 4-1 | Performance of software-based dynamic policies                           | 77  |

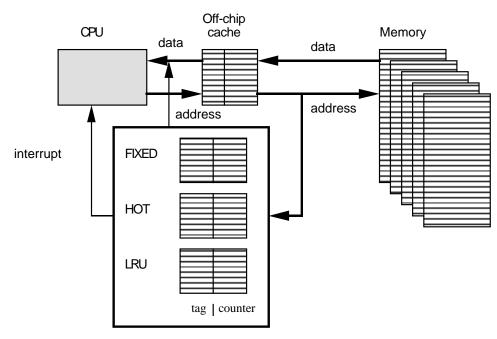

| 5-1 | The Cache Miss Lookaside Buffer.                                         | 89  |

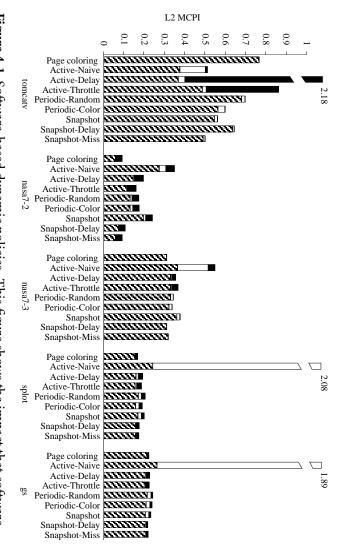

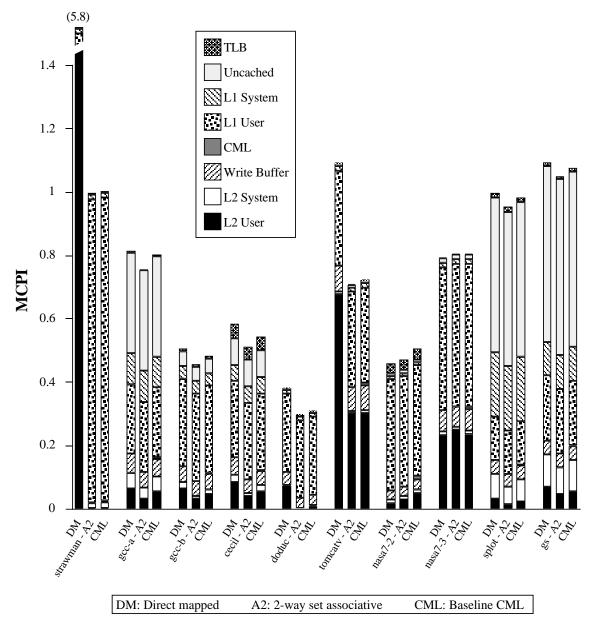

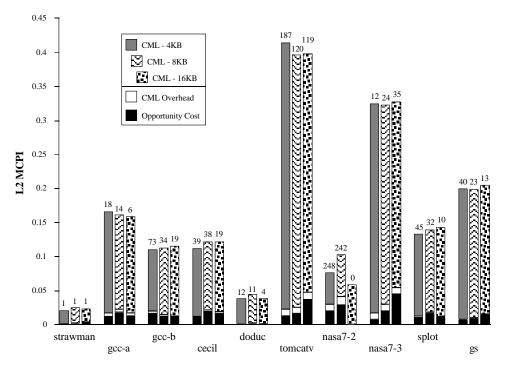

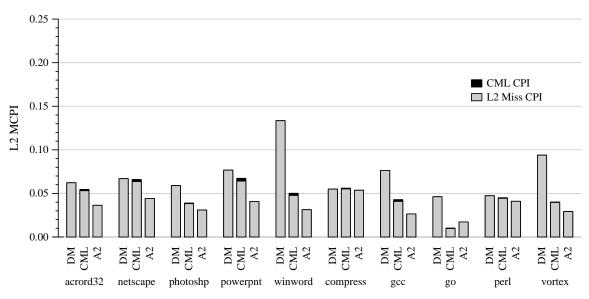

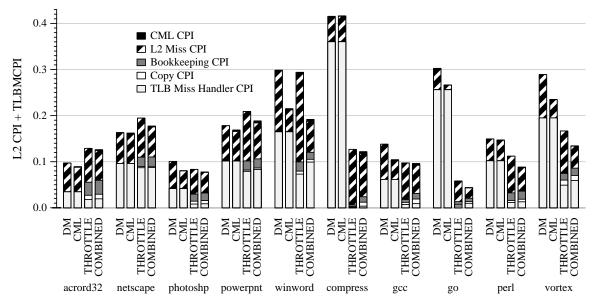

| 5-2 | Baseline memory system performance                                       | 95  |

| 5-3 | Performance of software-based and hardware-based dynamic mapping         |     |

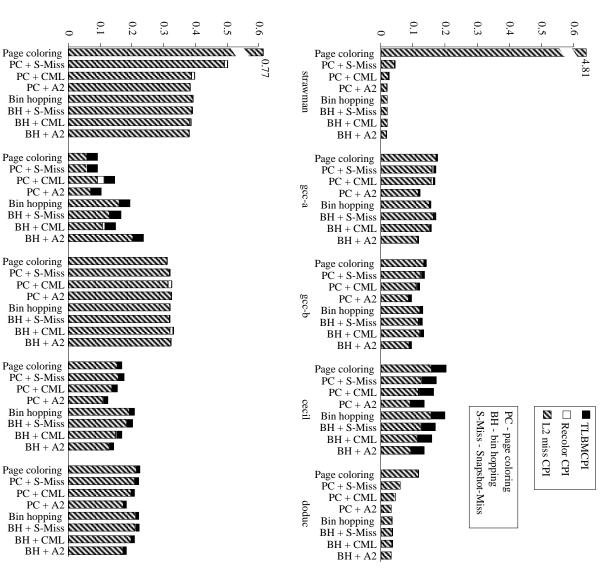

|     | policies.                                                                | 97  |

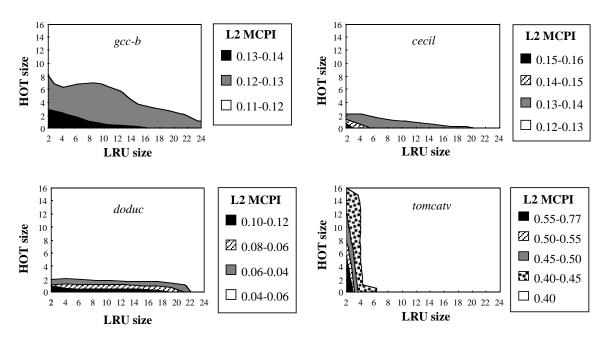

| 5-4 | Effect of varying CML buffer HOT and LRU sizes for four applications     | 103 |

| 5-5 | Stability of CML                                                         | 105 |

| 5-6 | Effect of page size on CML performance.                                  | 106 |

| 6-1 | The dilemma in choosing page sizes                                       | 111 |

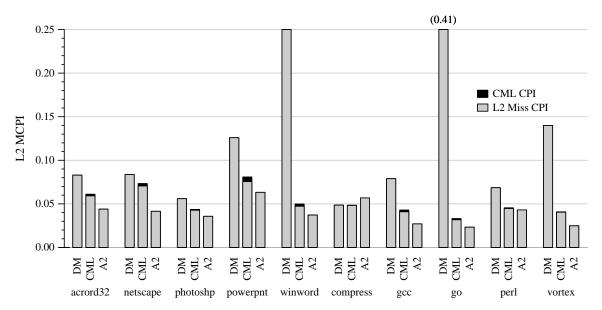

| 6-2 | Effect of the CML buffer on cache performance with an initial mapping of |     |

|     | page coloring                                                            | 119 |

| 6-3 | Effect of the CML buffer on cache performance with an initial mapping of |     |

|-----|--------------------------------------------------------------------------|-----|

|     | bin hopping.                                                             | 119 |

| 6-4 | Effect of superpage promotion on TLB performance                         | 120 |

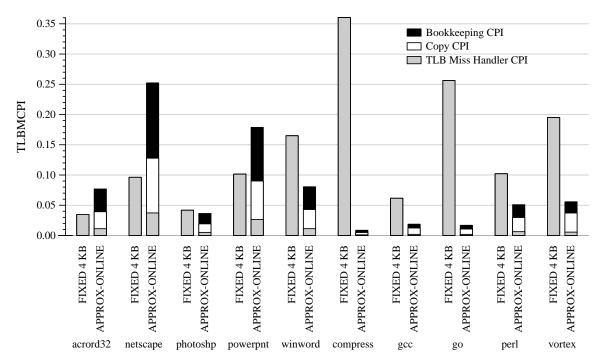

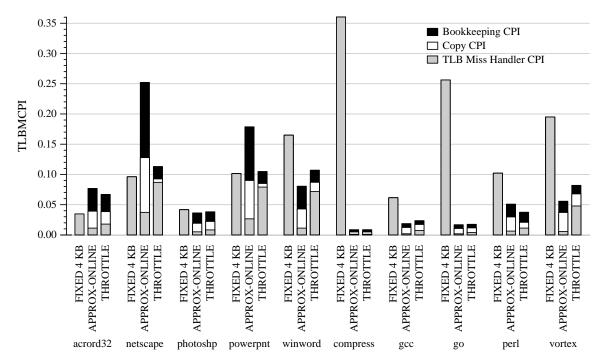

| 6-5 | Effect of superpage promotion with and without throttling on TLB perfor- |     |

|     | mance. For each application the effect of three policies on TLBMCPI is   |     |

|     | shown: a baseline policy that never promotes (FIXED 4KB), a superpage    |     |

|     | construction policy with no throttle (APPROX-ONLINE), and a superpage    |     |

|     | construction policy with a throttle ( <i>THROTTLE</i> )                  | 124 |

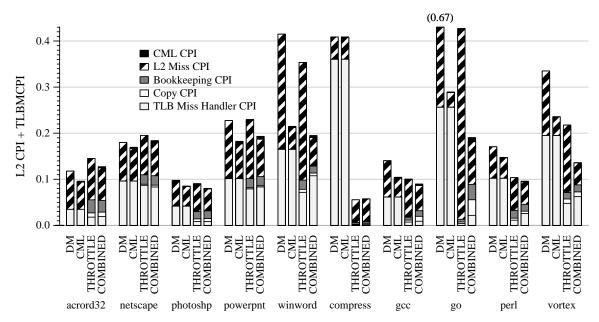

| 6-6 | Effect of COMBINED on cache and TLB performance with an initial map-     |     |

|     | ping of page coloring                                                    | 127 |

| 6-7 | Effect of COMBINED on cache and TLB performance with an initial map-     |     |

|     | ping of bin hopping.                                                     | 127 |

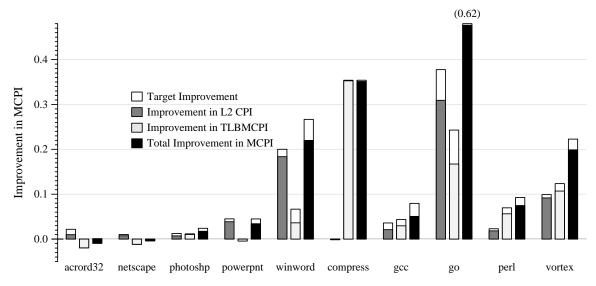

| 6-8 | Effect of combined cache and TLB optimization on MCPI with an initial    |     |

|     | mapping of page coloring.                                                | 131 |

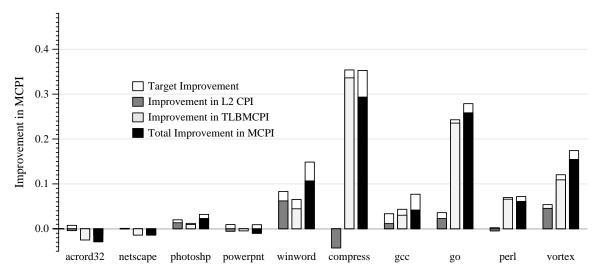

| 6-9 | Effect of combined cache and TLB optimization on MCPI with an initial    |     |

|     | mapping of bin hopping.                                                  | 131 |

## List of Tables

| 2-1 | Example TLB implementations.                                                 | 14  |

|-----|------------------------------------------------------------------------------|-----|

| 3-1 | Benchmark descriptions.                                                      | 24  |

| 3-2 | Baseline benchmark performance                                               | 25  |

| 3-3 | Cost of a single TLB miss for each policy                                    | 43  |

| 3-4 | Number of TLB misses using each policy.                                      | 44  |

| 3-5 | Estimated percentage improvement in end-to-end execution time                | 47  |

| 3-6 | Final page distributions for APPROX-ONLINE.                                  | 49  |

| 4-1 | Dynamic mapping policies.                                                    | 67  |

| 4-2 | Memory system parameters.                                                    | 71  |

| 4-3 | Benchmark descriptions.                                                      | 74  |

| 4-4 | Baseline memory system behavior                                              | 75  |

| 4-5 | Parameters of simulated dynamic mapping policies.                            | 76  |

| 4-6 | Performance of three cache management strategies                             | 79  |

| 4-7 | Overhead of dynamic policy operations                                        | 81  |

| 4-8 | Static vs. dynamic policies.                                                 | 83  |

| 5-1 | CML policy costs.                                                            | 94  |

| 5-2 | Break-even analysis of A2 and column-associative cache vs. CML               | 99  |

| 5-3 | Performance of DM, an eight entry victim cache, and CML                      | 100 |

| 6-1 | Windows/x86 benchmark descriptions.                                          | 115 |

| 6-2 | Simulated memory system parameters.                                          | 116 |

| 6-3 | Percentage of virtual pages copied by CML alone, by THROTTLE alone, or       |     |

|     | by both policies                                                             | 126 |

| 6-4 | Percentage of recolor operations due to virtual pages that were copied once, |     |

|     | twice, etc. by <i>COMBINED</i> with an initial mapping of page coloring      | 128 |

## Acknowledgments

In writing this thesis I enjoyed tremendous support from a wonderful group of friends and colleagues in Seattle and in the Computer Science and Engineering Department at the University of Washington. It is impossible to name them all here, or to even properly express my gratitude to those I do mention here. My advisor Brian Bershad helped me see the research I did in graduate school as a single body of work. Melody Kadenko-Ludwa helped me manage Brian. My other reading committee members-Anna Karlin and Hank Levy-helped improve the thesis significantly. My remaining thesis committee members—Craig Chambers, Susan Eggers, and Eve Riskin-also offered valuable advice. Several friends read and commented on drafts of the thesis, including Jonathan Shade, Sean Sandys, Dennis Lee, and Geoff Voelker. My research is at its best when it was collaborative: Brad Chen, Wayne Wong, Jean-Loup Baer, Alec Wolman, and Wayne Ohlrich, as well as Dennis, Geoff, Brian, Hank, and Anna were all co-authors on one or more papers. My late undergraduate advisor Louis E. Rosier was my first co-author and shared the joy of my first result. David Becker and Warren Jessop were always able to find me more disk space. No graduate student in the department prospers without the help of Frankye Jones, our academic advisor. John Wilkes at HP Labs waited, good-naturedly, while I finished my thesis.

My officemates over the past seven years offered many kinds of assistance, most of all in tolerating and even enjoying my "tedness" and in letting me "romer" their food: Neal Lesh is the best coffee drinker I've ever known; Jonathan let push him around; Sean changed the way I play Ultimate; Tashana Landray and Jake Cockrell provided the office Christmas tree; Wayne O. met me for breakfast every other Thursday; Dave Grove taught me how to deal with kegs of beer; Anthony LaMarca decorated the office with posters and plants and a dartboard and a velvet John Wayne; Mike Salisbury made the montage of childhood photos of the students in the office; and Jeff Dean shared his chips and salsa and Coke and technical insights.

Sung-eun Choi and E Chris Lewis and Ben Dugan and Jim Fix always tolerated my visits to their office. Sung surprised me with birthday and graduation gifts. Ruth Anderson helped me explore the parameters of the ski-rental problem in the real world. Nick Kushmerick and Marilyn McCune let me stay with them in Prague. Eric Anderson was always available to discuss matters technical and otherwise over beer. Brad Chamberlain was forgiving when I left school with his housekeys.

Finally, Shannon Creger provided support beyond anything I could have imagined as I finished writing, revising, and defending my thesis. My parents, Bob and Betty Romer, have always encouraged me throughout my diverse professional and personal pursuits. My late mother, Diana Romer, reminded me to trust my instincts.

Parts of this thesis have previously been published in somewhat different form. Chapter 3 is based on the paper "Reducing TLB and Memory Overhead Using Online Superpage Promotion" published in the *Proceedings of the 22nd Annual Symposium on Computer Architecture* [Romer et al. 95]. Chapter 4 is based on the paper "Dynamic Page Mapping Policies for Cache Conflict Resolution on Standard Hardware" published in the *Proceedings of the 1st USENIX Symposium on Operating System Design and Implementation* [Bershad et al. 94]. Chapter 5 is based on the paper "Avoiding Cache Misses Dynamically in Large Direct-Mapped Caches" published in the *Proceedings of the Sixth International Conference on Architectural Support for Programming Languages and Operating Systems* [Romer et al. 94]. In memory of my mother, Diana Haynes Romer.

## Chapter 1 Introduction

In this thesis I present operating system virtual memory policies that automatically, transparently, and dynamically improve the memory system performance of arbitrary userlevel programs. The policies are automatic in that they do not require any hints from the program about its memory reference patterns. The policies are transparent in that they do not require any change to the program's abstract model of storage, virtual memory. The policies are dynamic in that they observe and respond to changing application behavior as the program runs. The effect of these policies is to improve performance by matching application resource requirements and the available hardware resources.

The effectiveness of the memory hierarchy is a key element in the performance of computer programs. It has almost become an axiom of computer science that the time to access memory is increasing relative to the time to process instructions. For example, Hennessy and Patterson report that the gap between processor and memory performance is growing at 50% a year [Hennessy & Patterson 95]. To address the high cost of accessing memory, modern memory hierarchy implementations are becoming increasingly complex.

The focus this thesis is on the effect of caches and translation lookaside buffers (TLBs) on performance. Caches hold a subset of the contents of main memory in high speed storage, and TLBs hold a subset of operating system virtual to physical translations (page tables) in high speed storage. Application memory references that are satisfied by the cache avoid the penalty of accessing relatively slow main memory, and virtual addresses that can be translated by the TLB avoid a relatively slow page table lookup. Memory references that do result in cache or TLB misses, however, cost tens of processor cycles. Thus two key predictors of overall application execution time are the cache and TLB miss rates.

One indication of the importance of memory system performance is the increasing investment of both money and engineering effort to reduce the impact of high memory latency. An example of monetary investment in memory system technology is provided by Rambus, a corporation that produces and licenses technology for high bandwidth memory systems. The market capitalization of Rambus was \$1.8 billion as of August 22, 1997, reflecting a 580% increase since its initial public offering in May, 1997. An example of engineering investment in memory systems is provided by the Digital Alpha 21264 microprocessor [Keller 96]. This state-of-the art processor includes not just on-chip caches, but next line and set predictors (to reduce the average time to access first-level instruction caches), miss status holding registers (to allow the processor to continue to execute while satisifying cache misses), and prefetch instructions (to allow the compiler to hide the latency of memory references). Thus the stock market is willing to invest capital, and Digital (among other microprocessor manufacturers) is willing to invest engineering resources, in order to address the processor-memory performance gap. Like the solutions offered by Digital and Rambus, the policies introduced in this thesis can transparently improve the performance of arbitrary applications. Unlike those solutions, however, the policies in this thesis require only minimal changes to hardware processor and memory system designs.

Despite the importance of the memory system implementation to program performance, the details of cache and TLB configurations are hidden from user-level applications. While this aids portability, it can also hinder performance. Applications can make memory references that result in unnecessary cache or TLB misses. As a trivial example, a program might repeatedly generate references to two memory addresses that map to the same cache line. In a direct-mapped cache, only one of these two addresses can be in the cache, so the alternating references will result in cache misses. Even though the cache is large enough to hold both data items, the reference stream results in a large number of cache misses. This state of affairs is only revealed indirectly to the program or to the user in the form of long execution time. Only if the program is aware of the cache configuration will it be able to attribute the poor performance to the conflicting memory references.

This pathological example reveals both a problem and an opportunity. Because the user-level program is unaware of the details of the hardware, small problems such as this conflict may persist and result in significant performance bottlenecks. At the same time, the persistence of poor behavior means (1) that it is possible to detect problems and improve future performance by correcting the causes of the problems and (2) that it is acceptable for the detection and correction mechanisms themselves to have a high cost, as long as they have an even larger benefit.

The policies described in this thesis are targeted at memory system performance problems that result from the interaction of the software memory reference stream and the hardware implementation of the memory hierarchy, and that:

- have locality that is, they persist as the application runs;

- can be detected using feedback mechanisms; and

- can be corrected in the operating system by making more effective use of the cache and TLB.

The policies I present to solve these problems:

- rely on a combination of simple hardware support and operating system modifications to monitor the dynamic behavior of applications;

- use the information collected to identify sources of memory system delays such as cache misses and TLB misses;

- identify and resolve these bottlenecks, and as a result not only pay for the overhead of the monitoring mechanisms, but also significantly improve overall system performance; and

- require no changes to existing software or to existing CPU implementations.

The importance of such techniques will grow as the cost of accessing memory continues to increase relative to processor cycle time.

#### 1.1 Thesis statement and contributions

My thesis is that (1) effective management of hardware memory system resources requires dynamic detection, analysis, and correction of memory system bottlenecks, and that (2) the operating system is ideally situated to carry out these tasks. Static compiler-based techniques for improving memory system performance rely on programs with predictable reference patterns, cannot address resource conflicts that arise among multiple programs, require recompilation, and may be tailored to a specific memory system configuration. Purely hardware-based schemes are inflexible, in that the policies for analyzing and eliminating bottlenecks cannot be modified once the hardware is designed and built. In contrast, given appropriate feedback and control mechanisms, the operating system can implement software policies that are tailored to the characteristics of both the workloads and the hardware, and that can adapt dynamically as program behavior changes. The contributions of this thesis are to concretely demonstrate the opportunity to use the operating system to improve memory system performance.

- First, I introduce a policy that improves TLB performance by monitoring the TLB miss stream, analyzing the implied memory reference pattern of the workload, and then selectively constructing superpages. A superpage increases the granularity of virtual-to-physical translation, allowing a fixed-size TLB to map a larger portion of the virtual address space without a corresponding increase in physical memory requirements. This solution has three components: a feedback mechanism, namely notification of the location of TLB misses; a control mechanism, namely the ability to specify and construct superpages; and a superpage construction policy implemented in software.

- Second, I introduce operating system policies that eliminate cache conflicts in directmapped physically indexed caches by detecting pages that are suffering from cache conflicts and changing virtual to physical mappings to resolve the conflict. The goal of these policies is to arrange that active virtual pages are mapped to physical pages that do not conflict in the cache. The primary difficulty in implementing these policies is in designing appropriate feedback mechanisms. I introduce and evaluate two approaches to cache conflict resolution. One uses detection mechanisms based on existing hardware (TLB misses and cache miss performance counters), while the other uses proposed new hardware that precisely identifies the pages suffering from conflict misses. The details of the policies that interpret this feedback depend on the accuracy of the feedback mechanism. The control mechanism, in this instance, is the ability to transparently change virtual to physical mappings.

- Third, I analyze the interaction of these two techniques. The first technique relies on selectively increasing the page size in order to increase the coverage of the TLB. The second technique relies on a high degree of associativity in choosing the mapping from virtual to physical pages, but as the page size increases, this flexibility decreases. I show that despite this apparent conflict, the two techniques in fact complement one another. Using the two techniques together results in better performance than when using either technique alone.

Together, the contributions of this thesis illustrate the importance of using hardware feedback and control mechanisms and software operating system policies to analyze and eliminate memory system bottlenecks.

#### 1.2 Thesis overview

The rest of this thesis is organized as follows:

- Chapter 2 provides background information on the interaction of the virtual memory system, caches, and TLBs, and describes related work in this area.

- Chapter 3 describes a policy for dynamically constructing superpages in order to eliminate TLB misses without increasing the hardware TLB size or significantly increasing physical memory requirements.

- Chapter 4 describes how to detect and eliminate cache conflicts using standard hardware. Once conflicting pages are detected, the operating system can be remap them to physical pages that do not contend for the same location in a physically indexed cache.

- Chapter 5 describes how the approach described in Chapter 4 could be made more effective with the addition of a proposed simple hardware device, the Cache Miss Lookaside (CML) Buffer, that summarizes per-page miss counts.

- Chapter 6 considers the performance impact of a combined policy for superpage construction and cache conflict elimination, and also considers how the policies proposed in this thesis would affect the performance of Windows applications compiled for the x86 architecture.

- Finally, Chapter 7 summarizes and concludes.

#### THE PRINCIPLE OF LOCALITY

"She's made mistakes," he said. "So have I and so have you."

"At least I ain't made the same ones over and over agin," I said.

"Why not? You might as well make them you're used to as to make new ones all the time. It don't do no more damage."

Larry McMurtry, *Leaving Cheyenne*

### Chapter 2 Background and Related Work

The memory system optimizations introduced in this thesis draw upon and extend the efforts of many researchers to improve the design, implementation, and performance of the memory hierarchy. In this chapter I describe the basic operation of virtual memory, caches, and TLBs. I then discuss how prior research has sought to improve performance by exploiting the interactions between virtual memory and caches, and between virtual memory and TLBs. The work described in this thesis moves beyond the earlier research by showing how to manage cache and TLB resources dynamically rather than statically, thus allowing the system to adapt to changing application resource requirements.

As discussed in the introduction, the focus of this thesis is on policies that can be implemented in the operating system, without requiring changes either to on-chip hardware or to applications. Memory system optimizations that require specialized on-chip functionality are expensive and time consuming to implement. Optimizations that rely on algorithmic changes, program hints, or compiler support require varying degrees of programmer intervention, and may be limited to improving performance for specific hardware configurations. In this chapter, therefore, I describe background and prior work for cache and TLB performance optimizations that require little or no hardware support, that are programindependent, and that are automatic.

#### 2.1 Background

Before presenting more detailed background, I first give some intuition about how virtualto-physical mappings can affect cache and TLB performance.

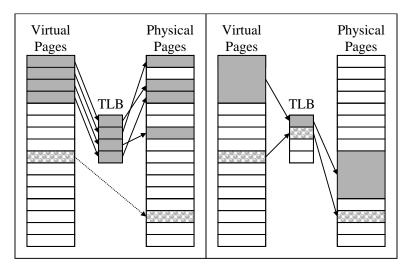

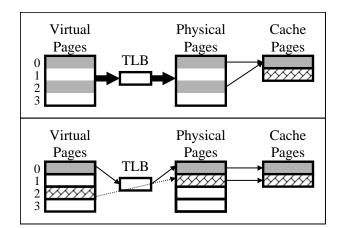

Figure 2-1 shows a simplified representation of the functionality of the TLB: it holds a subset of the mapping from virtual pages to physical pages, where a page is just a contiguous, aligned region of the address space. In the left half of the figure, five TLB entries are needed to map the application's working set. Four of the pages are contiguous and aligned in the virtual address space, but not in the physical address space. In the right half of the figure, the same virtual pages are in use, but now four of the pages are also aligned and con-

**Figure 2-1** Effect of page mappings on TLB performance. With appropriate virtual-tophysical mappings, the page size can increase, so that fewer TLB entries are needed to cover the same part of the virtual address space. In the mapping on the left, the four-entry TLB cannot cover the shaded virtual addresses. In the mapping on the right, the same virtual addresses are covered by just two TLB entries.

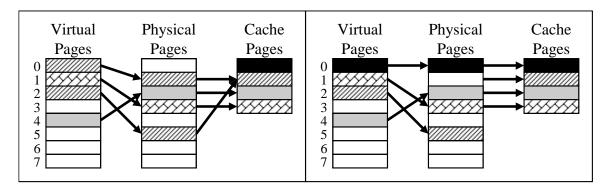

**Figure 2-2** Effect of virtual-to-physical mappings on cache performance. In the mapping on the left, two active virtual pages are mapped to the same cache page, so cache conflict misses can occur. In the mapping on the right, the set of active virtual pages is mapped to disjoint cache pages, so cache conflict misses cannot occur.

tiguous in the physical address space as well. If the TLB supports multiple page sizes, then a larger page can be used to map the group of four pages. The working set of the application can then be mapped with just two TLB entries, resulting in fewer TLB misses. In Chapter 3 I introduce dynamic virtual-physical mapping policies that transparently create large pages as needed. In Section 2.1.1 I provide more detailed background on the role of the virtual memory system in TLB performance and the opportunity to use superpages.

Figure 2-2 illustrates how virtual-to-physical mappings can affect cache performance. Again, the figure shows mappings from virtual pages to physical pages. In addition, the figure shows the mapping from physical pages to *cache* pages, page-sized regions of a physically indexed cache. Each cache page is assigned a different color, and each virtual page is given the color of the cache page to which it is ultimately mapped. Pages of different colors will never conflict in the cache. In the left half of the figure, pages 0 and 2 may conflict; but in the right half of the figure, with exactly the same set of virtual pages, no cache conflicts are possible. In Chapters 4 and 5 I will describe techniques for dynamically creating virtual-to-physical mappings like that in the right half of Figure 2-2 in order to reduce the number of cache conflicts. In Section 2.1.2 I provide more detail on the operation of caches and their interaction with the virtual memory system.

#### 2.1.1 Virtual memory, translation lookaside buffers (TLBs), and superpages

In order to understand the virtual memory management policies that I present later in this thesis, it is first necessary to understand the basic operation of virtual memory, and in particular to understand the role of page size in performance. For a more complete treatment of virtual memory the reader can consult standard references such as [Silberschatz & Galvin 97]. The material that I present here is intended only to provide enough background to motivate the use of multiple page sizes, page remapping, and dynamic superpage construction.

Modern computer systems provide user-level programs with an abstraction of storage called *virtual memory*. The program has uniform and exclusive access to a large *virtual address space*, typically 2<sup>32</sup> bytes (4 gigabytes) or more. In this thesis I am concerned with systems that implement *paged* virtual memory [Denning 70]. In a paged system, physical memory is used as a cache of virtual memory, and the size of the cache element is the virtual memory *page size*. Typically the page size is between 4 and 64 kilobytes (KB), and is fixed system wide. The status of each virtual page is tracked by operating system *page tables*. Each virtual page may be cached (*mapped*) by a page in physical memory, stored in secondary

storage such as a paging file on disk, or in some special state (*e.g.* invalid). The operating system is responsible for maintaining the page tables and other data structures that track the status of each virtual and physical page in the system. As long as the program refers only to virtual pages that are mapped to physical pages, it will have the illusion of fast exclusive access to large amounts of storage, even on a system with a small physical address space. When the program refers to virtual pages that are *not* cached in physical memory and must be fetched from the paging file, it is *paging*, and its performance will suffer since secondary storage is many orders of magnitude slower than physical memory.

r nysicai aduress

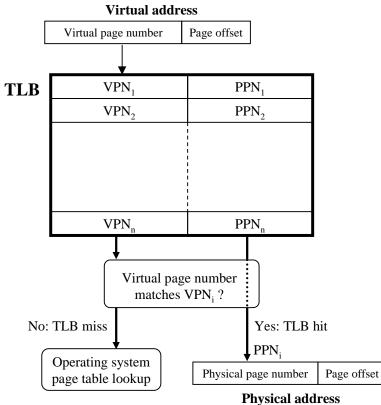

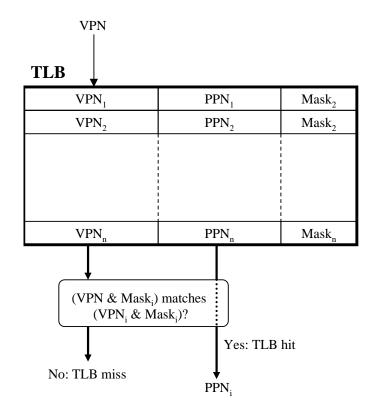

**Figure 2-3** A typical fully-associative software-filled TLB, with a single page size. On a reference to virtual address v, the virtual page number is used to access the TLB. If there is a TLB entry with a matching virtual page number, the physical page number is read from the TLB entry and combined with the page offset to form the physical address. The page number is simply the high order  $s - \log_2 p$  bits of the virtual address, where *s* is the number of bits in the address and *p* is the page size in bytes.

Because the implementation of virtual memory is transparent to applications, userlevel programs are unaware of the status of any particular virtual page. In particular, the operating system can choose an arbitrary physical page to back a given virtual page, or even change the physical page backing a virtual page while the application runs. Changing the virtual to physical mapping for a page, or *remapping*, requires three steps: (1) copying the data on the page to a free physical page; (2) updating the page table entry for the affected page to reflect the new virtual-to-physical mapping; and (3) freeing the original physical page. The policies introduced in this thesis rely on the ability to transparently remap pages.

While virtual memory is a great convenience to the programmer, it requires a virtualto-physical translation for each virtual address generated by the program. Conceptually this means consulting the page tables to find the physical page corresponding to the virtual page. To reduce the overhead of address translation, modern microprocessors include a hardware cache of recently translated pages called a translation lookaside buffer (TLB) (Figure 2-3). Addresses that hit in the TLB result in no delay, while addresses that miss in the TLB result in a page table lookup. The cost of a TLB miss is system-dependent, but as an example, on a DEC Alpha 3000/700 a TLB miss costs at least 31 processor cycles. Once the translation is found in the page tables it is inserted into the TLB, evicting some other translation according to the TLB's replacement policy. Some processors perform the page table lookup in hardware (for example, the Intel x86), while others rely on operating system software to perform the lookup (for example, the DEC Alpha, HP PA-RISC, and MIPS R4x00). The hardware approach can reduce the cost of each TLB miss, but constrains the operating system's implementation of page tables. In this thesis I will focus on softwarefilled TLBs, which notify the operating system on every TLB miss, and hence provide a straightforward feedback mechanism. The techniques described in this thesis could also be applied to systems with hardware-filled TLBs, although this would require a different feedback mechanism.

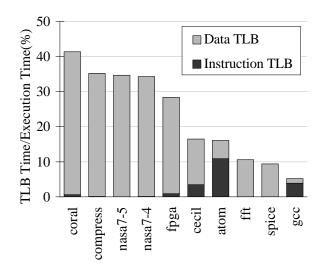

The *coverage* of the TLB is the product of the number of TLB entries and the operating system page size. When an application's working set is larger than the TLB's coverage, the resulting TLB misses can adversely affect application performance. For example, Figure 2-4 shows the percentage of execution time spent by various applications running on a DEC Alpha 3000/700 workstation. This system was running Digital Unix with fixed size 8 KB pages, and is based on a DEC Alpha 21064 processor, with a 32 entry fully associative TLB for data and an 8 entry fully associative TLB for instructions. The coverage of the data TLB is therefore just 512 KB. Because the data working set of most of these applications is much larger than 512 KB, the applications incur a large number of TLB misses as they run. Coupled with a TLB miss penalty of 31 cycles, the high TLB miss rates result in the

**Figure 2-4** Effect of TLB misses on performance on a DEC Alpha 3000/700. This graph shows the percentage of execution time spent handling TLB misses. The data was collected by instrumenting the TLB miss handler with calls to the hardware cycle counter. For additional information on the system under test and the workloads, see Chapter 3.

significant performance degradation illustrated by the figure.

One way to increase the coverage of the TLB and deal with this performance problem is to devote additional hardware resources to the TLB. For example, the follow-on to the 21064, the DEC Alpha 21164, expanded the TLB to 64 entries for data and 48 entries for instructions, doubling the coverage of the data TLB (the primary source of TLB misses for these applications). However, such hardware solutions may increase the time to access the TLB for all references, not just misses; furthermore, merely doubling the TLB size is insufficient for many memory-intensive applications.

Another way to increase the TLB coverage is to increase the operating system page size. However, larger pages can result in inefficient use of physical memory. For example, if a program uses only two words that are widely separated in the virtual address space, two entire physical pages must be allocated to map the two corresponding virtual addresses. The larger the page size, the more memory will be wasted due to internal fragmentation. Inefficient use of memory, in turn, can result in paging – if the working set of the application no longer fits in main memory it must in part be stored on secondary storage.

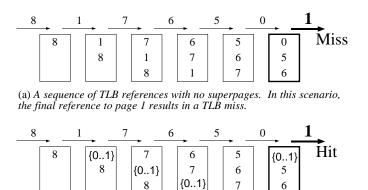

In contrast, the operating system policies that I describe in this thesis can increase the coverage of a given sized TLB by much more than a factor of two, without requiring changes to existing TLB implementations. In particular, these policies take advantage of TLBs that support variable page sizes, or *superpages*. Variable page sizes offer an opportunity to in-

**Figure 2-5** A typical TLB, with support for multiple page sizes (superpages). Each TLB entry includes an additional field corresponding to the page size. Conceptually the field is simply a mask *m*, which indicates which of the bits in the virtual page number are used to detect a match on a reference to the TLB. On a reference to virtual page *v*, a TLB hit occurs if there is a TLB entry for virtual page v' with mask *m'* such that v & m' = v' & m', where & is the bit-wise AND operation.

crease TLB coverage without incurring the internal fragmentation that would accompany a global increase in the page size. A superpage is a page with a size that is a power of two multiple of the minimum page size, and that is contiguous and aligned in both the virtual and physical address spaces. Each page table entry and TLB entry is augmented with a field that indicates how large the page is or equivalently, how many bits of the virtual address make up the page number (Figure 2-5). One implication of supporting variable page sizes in the TLB is that the TLB must be fully associative [Talluri 95]. Many current processor architectures support multiple page sizes, including the DEC Alpha, the PowerPC, the Intel Pentium, the Sun UltraSparc, and the HP Precision. The range of page sizes varies from system to system; some examples are shown in Table 2-1. **Table 2-1** Example TLB implementations. This table shows the parameters of the TLB implementations on some current microprocessors. Four of the processors shown have support for multiple pages in the primary TLB, while two (the PowerPC and the Pentium Pro) support a single page size in the primary TLB and have auxiliary hardware to support large pages.

| Processor                  |          | Primary TLB                                  |          | Auxiliary TLB           |

|----------------------------|----------|----------------------------------------------|----------|-------------------------|

|                            | TLB size | Page size(s)                                 | TLB size | Page size(s)            |

| IBM PowerPC 603e [IBM 95]  | 64I+64D  | 4 KB                                         | 4I+4D    | 128 KB, 256 KB,, 256 MB |

| Intel Pentium Pro [Int 97] | 32I+64D  | 4 KB                                         | 4I+8D    | 4 MB                    |

| Alpha 21164 [Dig 97]       | 48I+64D  | 8 KB, 64 KB, 512 KB, 4 MB                    |          | not applicable          |

| HP PA-8000 [Hunt 95]       | 96       | 4 KB, 16 KB, 64 KB, 256 KB, 1 MB, 4 MB, 8 MB |          | not applicable          |

| MIPS R10000 [Heinrich 96]  | 64       | 4 KB, 16 KB, 64 KB, 256 KB, 1 MB, 4 MB, 8 MB |          | not applicable          |

| UltraSparc II [Sun 97]     | 64I+64D  | 8 KB, 64 KB, 512 KB, 4 MB                    |          | not applicable          |

#### 2.1.2 Caches and virtual memory

The policies that I present in this thesis for improving cache performance exploit the interaction between operating system virtual-to-physical mappings and cache conflict misses. This section provides background on the operation of caches and gives a simple example of the effect of virtual to physical mappings on cache behavior. As with virtual memory systems, a complete treatment of caches is beyond the scope of this thesis, and the reader is referred to the literature for additional background [Smith 82, Hennessy & Patterson 95].

A cache consists of high-speed memory that holds a subset of the data in virtual or physical memory. The cache is divided into cache *lines*, typically between 16 and 64 bytes. On a memory reference, the address is divided into three fields. The low order bits are the offset of the data within the cache line. The middle bits are used to index into the cache. A cache is called *virtually indexed* or *physically indexed* depending on whether the virtual or physical address is used to index into the cache. Virtually indexed caches have the advantage of not requiring an address translation before the cache lookup, but have the disadvantage of introducing aliases (a single virtual address referring to a single physical address).

The high order bits of the address are the tag, and are used to distinguish addresses that index to the same cache location. If the address tag and the tag stored in the cache line match, then the reference is a cache hit. Otherwise, the reference is a miss, and the data must be fetched from the next level in the memory hierarchy. In a direct-mapped cache, each memory address maps to exactly one cache line. In an *n*-way associative cache, each address can map to any one of *n* lines.

Cache conflict misses occur because previously referenced data has been displaced by

data that maps to the same cache location. For example, when the cache is large enough to hold the data in use, but the data is unfortunately mapped to lines that contend for the same cache locations, cache misses will occur. Such conflict misses could be prevented with a different mapping of addresses to cache lines.

In a physically indexed cache, the mapping from physical addresses to cache lines is fixed by the hardware cache index function. The mapping from *virtual* addresses to cache lines, though, is controlled by the combination of the operating system's virtual-to-physical mappings and the hardware cache index function. As a result, cache conflicts in a physically indexed cache are in part due to the operating system's assignment of physical pages to virtual pages. The virtual memory page size partitions a direct-mapped physically indexed cache into a set of *cache pages* [Wheeler & Bershad 92]. The set of physical pages, in turn, is partitioned into multiple equivalence classes, or *colors*, where pages of the same color map to the same cache page. Conflicts can only occur between pages of the same color, and no conflicts can occur within a single page as long as the page size is not larger than the cache size.

Any virtual-to-physical mapping that assigns the active virtual pages to physical pages of different colors pages is optimal in that it avoids conflict misses. A mapping that assigns two or more virtual pages to the same color may not be optimal and can induce cache conflict misses. For example, Figure 2-2 showed a "good" and a "bad" mapping for the same set of virtual pages. In the good case, the active virtual pages all map to different cache pages, so no cache conflict misses are possible. In the bad case, two of the virtual pages map to the same cache page, so addresses at the same offset within the two pages will contend for the same cache lines, resulting in conflict misses. In Section 2.2.2, I describe some common static mapping policies that use heuristics to avoid cache conflicts. Since these policies are static, however, they cannot be adjusted if the working set of the application changes or if the heuristic turns out to be inappropriate. As mentioned in the virtual memory section above, it is possible to change virtual to physical mappings transparently to the application. Later in this thesis I will introduce policies that take advantage of this opportunity to eliminate cache conflicts due to poor virtual to physical mappings.

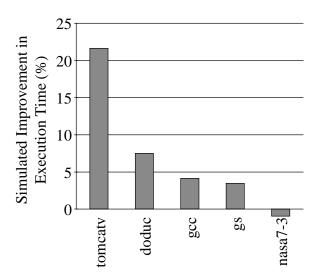

The impact of cache conflict misses on application performance is illustrated by Figure 2-6. The figure shows the simulated improvement in execution times that result from replacing a direct-mapped cache with a two-way associative cache with the same size and access time. Unfortunately, real associative caches have higher cost and higher access time than a direct-mapped cache of the same size [Wood 86], so these results may not be attain-

**Figure 2-6** Effect of conflict misses (simulated). This graph shows the predicted improvement in execution time by replacing a direct-mapped off-chip cache with a hypothetical two-way associative cache with the same size (512 KB) and access time. The simulated memory system is based on the DEC Alpha 3000/500. The reduction in execution time indicates the opportunity to improve performance by eliminating cache conflicts. For further details on the simulation and the workloads, see Chapter 4.

able in practice. The goal of the policies introduced in this thesis is to use operating system virtual-to-physical mapping policies to eliminate cache conflicts in software without incurring the costs of hardware associativity.

#### 2.2 Related work

In this section I briefly describe prior research based on the observation that the operating system's virtual memory policies affect cache and TLB performance. These techniques generally consist of finding static virtual-to-physical mappings that result in relatively good memory system performance. This thesis shows that by changing page sizes and virtual-tophysical mappings as a program runs, performance can be improved even further.

#### 2.2.1 TLB management

A number of researchers have noted that large pages could improve the TLB performance of applications with large working sets. Most have proposed user-level policies for setting the page size, but have not actually demonstrated the effectiveness of such policies:

- Harty and Cheriton[Harty & Cheriton 92] propose mechanisms that would allow an application to manage its own physical memory, including varying the page size within segments of its address space. They do not discuss policies for selecting page sizes. Implementing the superpage construction policies described in this paper could use their mechanisms for controlling page sizes, but would require extensions to provide feedback on TLB performance to the application.

- In Chen *et al.*'s study of TLB performance [Chen et al. 92], the authors suggest using compiler feedback to identify regions of the program text that could be mapped by larger pages, and tuning memory allocation algorithms to map frequently used data to contiguous regions in order to facilitate the use of large pages. They do not evaluate these proposals, however.

- Mogul [Mogul 93] also suggests using large pages to increase TLB coverage. He describes qualitatively the tradeoffs involved in constructing superpages dynamically, and suggests this as a possible research direction.

Talluri *et al.* [Talluri et al. 92, Khalidi et al. 93, Talluri & Hill 94, Talluri 95, Talluri et al. 95] go further, proposing techniques that use the operating system to improve TLB performance without requiring user-level intervention. They consider superpages, but focus on proposed *partial subblock TLBs*. A subblock TLB, akin to a subblock cache [Hennessy & Patterson 95], has multiple entries associated with each tag. For example, in a TLB with base page size of 4 KB and subblock factor 16, a single TLB entry could map a contiguous aligned region of the virtual address space as large as 64 KB.

As with superpages, for partial subblock TLBs to be effective the operating system must map contiguous aligned regions of virtual memory to contiguous aligned regions of physical memory. Subblock TLBs have less stringent requirements than superpage TLBs, however. If one or more of the component virtual pages cannot be represented by the shared TLB entry (because it differs in protection or validity, or because it is mapped to a different part of the physical address space), it can be marked invalid and mapped with a separate TLB entry. To arrange that pages are aligned and contiguous in the virtual and physical address spaces, Talluri *et al.* propose an operating system policy of *page reservation* to support superpage and subblock TLBs. The virtual and physical address spaces are divided into 64 KB regions; the operating system makes a best effort to allocate virtual pages in one 64 KB region to physical pages in one 64 KB physical region. This reservation policy can allow the creation of superpages with no runtime cost, and similarly can allow a single subblock TLB entry to map a large number of 4 KB pages. However, it restricts the freedom of the virtual memory system to map virtual pages to specific physical pages (to avoid cache conflicts), and effectively constrains the operating system to allocate pages in 64 KB regions, regardless of the actual access patterns of the application. As a result, this policy may needlessly fragment the physical address space. Specifically, reservation makes it difficult to construct superpages of varying size, since there is no way to decide *a priori* how many base pages to reserve at page allocation time. For small superpages, reservations may often hold until they are needed. As the superpage size grows, however, it is increasingly likely that a reservation will fail: that is, some base page within the reserved superpage is allocated for another purpose before the superpage is actually created.

Talluri *et al.*'s primary interest is in measuring the effectiveness of subblock TLBs. However, they do propose one superpage policy simply to provide a point of comparison. This policy creates a superpage as soon as some fraction of the component pages have been referenced. They do not explore the design space of this policy, nor do they consider policies that copy pages dynamically in order to create superpages at runtime. In effect, superpages are created only if the original reservation was successful. Both their superpage and subblock TLB policies effectively limit the maximum page size to 64 KB, and would be ineffective for applications with working sets larger than would be mapped by a TLB with 64 KB pages. They suggest that larger pages can be created in response to application hints, but do not consider using larger pages for arbitrary applications.

#### 2.2.2 Virtual memory mapping policies

Several other researchers have investigated the impact of the operating system's virtual-tophysical mapping policies on both cache performance and address translation performance. Cache performance is affected by mapping policies as described in Section 2.1.2. As a result, prior research has focused on techniques for mapping simultaneously active virtual pages to physical pages of different colors. Knowing the operating system mapping policy in advance can allow optimizations in the implementation of address translation hardware.

#### Page coloring

The work of Chiueh and Katz [Chiueh & Katz 92], Taylor [Taylor et al. 90], and Lynch [Lynch 93] is based on a simple static mapping policy called *page coloring*. Page

coloring assigns virtual pages to colors in a round robin fashion, assigning virtual page 0 to the first color, virtual page 1 to the second color, and so on. (To avoid inter-address space conflicts, different permutations of the color order can be used for different processes — for example, by hashing the virtual page number with the process identifier to determine the color.) This heuristic has the virtue that pages close together in the virtual address space will not conflict in the cache.

Generally page coloring is not strictly enforced by the operating system: if there is no free page of the desired color, a free page of another color is chosen. However, Lynch, in his thesis on the cache performance of various static page allocation policies, focuses on "perfect coloring," in which the operating system does enforce page coloring strictly. Perfect coloring has the advantage of allowing the placement of virtual pages in the cache to be easily controlled at user-level, and can allow the index into a physically indexed cache to be computed from the virtual address without performing address translation (since the low order bits of the physical page number are determined by the virtual page number.) Unfortunately, by constraining the associativity of the mapping from virtual to physical pages, perfect coloring may result in increased paging rates. Since fetching a page from secondary storage is many orders of magnitude more expensive than a cache miss, real systems do not implement strict page coloring.

Both Chiueh *et al.* and Taylor *et al.* consider how to reduce the hardware needed for address translation when the operating system attempts to map pages according to the page coloring heuristic. While the two papers propose different mechanisms, the basic observation is that in the presence of page coloring, the low order bits of the virtual page number are a good predictor for the low order bits of the physical page number. Taylor *et al.* exploit this observation in their design of the "TLB slice." The TLB slice is a hardware table that provides a translation hint for just the low order bits of the virtual page number in order to generate the index into a physically indexed cache. This allows a virtually-tagged, physically indexed cache to be accessed without performing a full TLB lookup. Page coloring helps the performance of the TLB slice by allowing multiple virtual pages to share a single entry in the table.

#### Other static mapping policies

Kessler *et al.* [Kessler & Hill 92] considered static page mapping policies that use varying degrees of sophistication to avoid conflicts in a physically indexed cache. They provide an excellent overview of the interaction of page mapping policies and cache performance. They introduce several "careful" mapping policies that use heuristics to avoid cache hot spots. They find that sophisticated policies that try to measure the number of pages allocated to any color provide some minor performance advantages. However, for the workloads under study a simple *bin hopping* heuristic works nearly as well as policies that maintain much more information about past allocation decisions. Bin hopping assigns virtual pages to colors cyclically according to the order in which they are initially mapped. This policy has the virtue that pages initially referenced close together in time will be assigned to different colors and hence will not conflict in the cache. In addition, it is feasible for user-level applications to manipulate the cache placement of virtual pages by controlling the order in which they initially reference pages [Bugnion et al. 96].

## Dynamic mapping policies

Finally, Sites [Sites 95] proposes a technique for changing virtual-to-physical mappings in response to application cache miss behavior. This technique is based on hardware that effectively records the address of every cache miss. By periodically sampling the cache miss address, the operating system can identify pages suffering from large numbers of misses. Depending on the cause of the cache misses, such pages can be migrated (to reduce coherence misses on a multiprocessor) or remapped (to eliminate cache conflicts). A potential disadvantage of this policy is that the sampling technique may allow a large number of cache misses to occur before the offending pages are identified and remapped or migrated. In contrast, the techniques that I propose in Chapter 5 can identify conflicting pages after a relatively small number of cache misses.

# 2.3 Evaluation of prior work

While the prior research in this area has demonstrated some performance benefits, it falls short of the potential for operating system virtual memory policies to eliminate cache and TLB misses. The fundamental shortcoming of all of the preceding work, except for Sites's proposal, is that it attempts to derive *static* solutions to what are inherently *dynamic* performance problems. Application memory reference patterns are difficult to predict statically, so optimizing memory system performance for general purpose applications requires dynamic analysis of application behavior. Static mapping policies cannot adapt as the working set of an application changes. There is a class of scientific codes that do have relatively predictable reference patterns, and a body of work devoted to the automatic optimization of memory use for these applications. But even for these applications, static memory management policies cannot detect contention between different applications for memory system resources, or between the operating system and user-level programs [Mogul & Borg 91, Chen 94].

Another optimization technique is to use profiles of past runs to predict the behavior of future runs. The appeal of this approach is that if future behavior is identical to past behavior, it should be possible to use profile information to provide optimal performance. Unfortunately the resulting optimizations will be specific to the program, to the input stream, and to the hardware platform. Attaining the maximum benefit from profiledriven optimization would require case-by-case profiling and optimization for each program, for each hardware platform, and for each input stream. In contrast, the techniques developed in this thesis seek to obtain the benefit of such custom optimizations while using generic policies that apply to all programs and platforms. These policies effectively profile and optimize performance dynamically, obtaining the benefits of profile-driven optimization as programs run rather than afterwards. Although application-specific optimizations will always perform at least as well as generic optimizations, the techniques proposed here often perform as well or nearly as well as optimizations that have exact information about the program's reference patterns, at a far lower implementation cost.

Drawing an analogy from the hardware domain, a cache is a simple and effective device that adapts at runtime to application reference patterns. A cache works because it takes into account the past behavior of the application, and uses the principle of locality to predict (usually correctly) that recently referenced addresses will be referenced again in the near future. However, a cache only considers a very small window onto the application's memory reference stream. As the cost of memory accesses increases relative to processor speed, it will become increasingly attractive to collect more detailed information and employ more sophisticated run time analysis to better manage the memory hierarchy. This thesis, then, explores how to apply the principle of locality within the operating system's virtual memory system to detect and eliminate cache and TLB misses.

In the remainder of this thesis I will describe techniques that go beyond the prior work by taking advantage of dynamic information about application memory reference patterns, and use this information to transparently remap pages, optimizing page sizes and page mappings to eliminate TLB misses and cache conflict misses. The policies introduced in this thesis rely on runtime analysis to trade off the cost of remapping pages with the expected benefits from reduced miss rates. They do not require changes to on-chip hardware, nor are they specialized to particular applications. The net result is operating system virtual memory policies that match the memory system resource requirements of existing applications to the resources available on existing hardware, improving upon static mapping policies in terms of memory consumption, overall execution time, or both.

# Chapter 3 Using Virtual Memory to Improve TLB Performance

# 3.1 Introduction

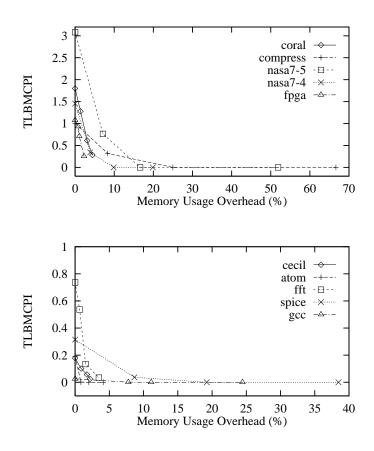

In this chapter I show how to use the operating system to improve application execution time by dynamically managing the memory system resources provided by the TLB. The techniques I describe rely on variable size pages — superpages — to increase the coverage of the TLB and hence reduce TLB miss rates. A naive strategy for using superpages to improve TLB performance would be to use large pages throughout the address space. While this strategy would increase TLB coverage by increasing the amount of memory mapped by each TLB entry, the internal fragmentation of the large pages would cause memory consumption to increase relative to a system that used only small pages. The contribution of this chapter is to introduce a policy that selectively creates superpages at runtime, providing the good TLB coverage of large pages and the good memory consumption of small pages.

TLB performance can have a dramatic effect on application execution time. To quantify this effect, I measured the percentage of execution time spent handling TLB misses for a collection of programs running on a DEC Alpha 3000/700. (These programs are used as benchmarks throughout this chapter, and are described in Table 3-1.) Table 3-2 shows the results of this experiment: the applications spent between 5.2% and 41.4% of their time in the TLB miss handler.